## Underside Federal de Juiz de Fora Programa de Pós-Graduação em Engenharia Elétrica

Guilherme Márcio Soares

# CAPACITANCE REDUCTION IN OFF-LINE LED DRIVERS BY USING ACTIVE RIPPLE COMPENSATION TECHNIQUES

Tese de Doutorado

Juiz de Fora 2017 Guilherme Márcio Soares

Capacitance Reduction in Off-line LED Drivers by Using Active Ripple

Compensation Techniques

Tese submetida ao corpo docente da coorde-

nação do Programa de Pós Graduação em

Engenharia Elétrica, área de concentração:

Sistemas Eletrônicos, da Faculdade de Engenharia da Universidade Federal de Juiz de

Fora como parte dos requisitos do curso de

doutorado em engenharia elétrica.

Orientador: Prof. Henrique Antônio Carvalho Braga, Dr. Eng.

Coorientador: Prof. José Marcos Alonso Alvarez, Dr. Eng.

Juiz de Fora

2017

Ficha catalográfica elaborada através do programa de geração automática da Biblioteca Universitária da UFJF, com os dados fornecidos pelo(a) autor(a)

Soares, Guilherme Márcio.

Capacitance Reduction in Off-line LED Drivers by Using Active Ripple Compensation Techniques / Guilherme Márcio Soares. -- 2017.

287 p.

Orientador: Henrique Antônio Carvalho Braga Coorientador: José Marcos Alonso Alvarez Tese (doutorado) - Universidade Federal de Juiz de Fora, Faculdade de Engenharia. Programa de Pós-Graduação em Engenharia Elétrica, 2017.

1. Conversores para o acionamento de LEDs. 2. Compensação de ondulação de corrente. 3. Redução de capacitâncias. 4. Otimização de conversores estáticos. 5. Correção do fator de potência. I. Carvalho Braga, Henrique Antônio, orient. II. Alonso Alvarez, José Marcos, coorient. III. Título.

## Guilherme Márcio Soares

Capacitance Reduction in Off-line LED Drivers Using Active Ripple Compensation Techniques

Tese submetida ao corpo docente da coordenação do Programa de Pós Graduação em Engenharia Elétrica, área de concentração: Sistemas Eletrônicos, da Faculdade de Engenharia da Universidade Federal de Juiz de Fora como parte dos requisitos do exame de qualificação do curso de doutorado em engenharia elétrica.

Aprovada em 18 de novembro de 2017.

BANCA EXAMINADORA:

Prof. Henrique Antônio Carvalho Braga, Dr. Eng.

Universidade Federal de Juiz de Fora, UFJF

Prof. José Marcos Alonso Álvarez, Dr. Ing.

Universidade de Oviedo, UNIOVI

Prof. Marco Antônio Dalla Costa, Dr.

Universidade Federal de Santa Maria, UFSM

Prof. Edilson Mineiro Sá Júnior, Dr. Eng.

Instituto Federal de Educação, Ciência e Tecnologia do Ceará, IFCE

Prof. Pedro Gomes Barbosa, Dsc.

Universidade Federal de Juiz de Fora, UFJF

Prof. Leonardo Willer de Oliveira, Dsc.

Universidade Federal de Juiz de Fora, UFJF

## ACKNOWLEDGMENT

This work is the result of the contribution of several people, and without them, it would not be developed in the way it was. Because of this, I need to make a brief acknowledgment.

First of all I thank God and his son, Jesus Christ, who were my first great teachers.

To my parents, because they supported me in the most difficult moments. I also thank my sister for her companionship during all these years.

To my girlfriend Camila, for the affection and understanding during this journey.

To all the professors of the electrical engineering course of the Federal University of Juiz de Fora, who shared their knowledge and helped in my professional growth. I am especially grateful to professor Henrique Braga, my supervisor, for the opportunity to research and make science. Furthermore, I thank professor José Marcos Alonso, my co-supervisor, which had a major contribution in this thesis and was very kind to me at the time I was in Gijón-ES.

To my colleagues of the Lighting Research Group (NIMO-UFJF), because this work also has a contribution of each one of them.

Finally, to my friends, for being with me in difficult times.

#### **RESUMO**

Este documento apresenta uma nova técnica para a minimização da ondulação de baixa frequência, típica de conversores para o acionamento de LEDs alimentados a partir da rede elétrica. Esta estratégia baseia-se na modulação em baixa frequência da razão cíclica do conversor de modo que a ondulação de corrente possa ser reduzida e, consequentemente, as capacitâncias de filtragem do conversor possam ser minimizadas. Esta técnica foi desenvolvida para a aplicação em conversores de malha única, como é o caso de conversores de estágio único ou mesmo dois estágios integrados. A modulação da razão cíclica é projetada de maneira que o comportamento de baixa frequência das principais variáveis do conversor seja alterado, permitindo uma redução da ondulação da corrente de saída ao custo de um incremento cotrolado no conteúdo harmônico da corrente de entrada. Duas possíveis metodologias para a implementação da técnica proposta são discutidas ao longo do trabalho. A primeira envolve a injeção de harmônicas específicas no sinal da razão cíclica do conversor através de ramos adicionais na estrutura de controle. Esta abordagem foi aplicada para projetar um controlador de LEDs baseado em um conversor flyback e também em uma topologia integrada baseada na conexão cascata de dois conversores buck-boost. Este estudo inicial foi expandido para outros conversores e uma análise generalizada acerca da influência da modulação da razão cíclica no comportamento de controladores de LED alimentados a partir da rede elétrica é apresentada. A segunda metodologia para a implementação da compensação ativa da ondulação de baixa frequência do conversor é baseada na otimização de um controlador proporcional-integral a fim de que tal elemento influencie não só no comportamento dinâmico do circuito, mas também na caracteística de baixa frequência do conversor. Por fim são discutidas as principais contribuições da tese e algumas propostas para trabalhos futuros são apresentadas.

Palavras-chave: conversores para o acionamento de LEDs, fontes de alimentação, conversores alimentados a partir da rede elétrica, compensação ativa da ondulação de baixa frequência, redução de capacitâncias, correção do fator de potência, conversores sem capacitores eletrolíticos, fontes de alta confiabilidade, otimização de conversores estáticos.

## ABSTRACT

This document presents a novel approach for low-frequency output current ripple minimization in off-line light-emitting diode (LED) drivers. This strategy is based on the large-signal modulation of the duty-cycle so that the output ripple can be reduced and, consequently, the required filtering capacitances of the converter can be somehow decreased. This technique is devised to be used on converters in which a single control loop is employed, such as off-line single-stage or integrated converters. The duty-cycle modulation is used to change the shape of the main waveforms of the converter, especially the input and output currents. This allows for a reduction of the output current peak-to-peak ripple while the harmonic content of the input current is increased but kept within the limits imposed by the IEC standard. Two methodologies for implementing the proposed technique are discussed along the text. The first one is related to the injection of harmonic components to the duty cycle signal by means of additional branches inserted in the conventional control structure. This approach was applied to design an off-line flyback-based LED driver and also a circuit based on the Integrated Double Buck-boost converter. This first study was expanded to other topologies and a generalized analysis regarding the impact of the duty cycle modulation on off-line converters is then presented. The second methodology for implementing the ripple compensation is based on the optimization of a proportional-integral controller so that this element is designed to influence not only in the dynamic behavior of the circuit, but also in its low-frequency characteristic. Finally, the main contributions of this work are discussed and the proposals for future works are presented.

Keywords: LED drivers, power supplies, off-line operation, active ripple compensation, capacitance reduction, power factor correction, electrolytic capacitor avoidance, high reliability, power converter optimization.

## LIST OF ILLUSTRATIONS

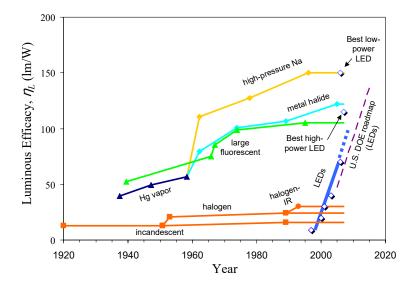

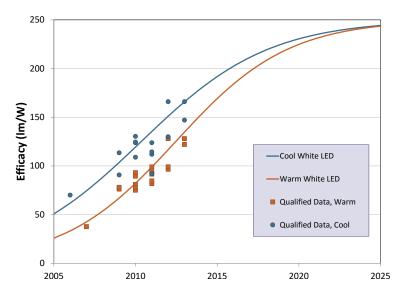

| Figure 1  | Evolution of the luminous efficacy of several lighting sources. (CRAFORD, 2007).                                                                                                                                                          | 36 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | White-light phosphor-converted LED projections for commercial products. (BARDSLEY et al., 2014b).                                                                                                                                         | 36 |

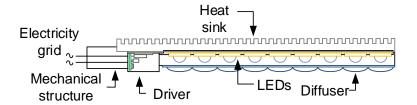

| Figure 3  | Main components of an LED luminaire.                                                                                                                                                                                                      | 37 |

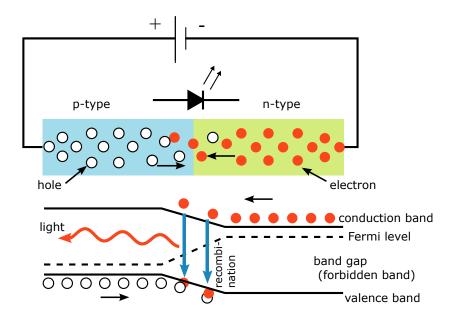

| Figure 4  | Diagram of a light emitting diode. (S-KEI, 2011).                                                                                                                                                                                         | 37 |

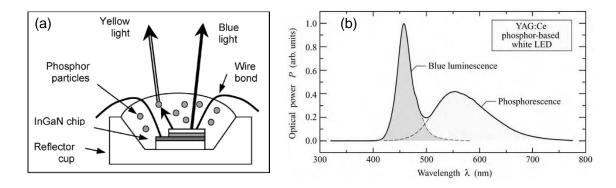

| Figure 5  | Phosphor-converted Light-emitting Diode (LED). (a) Working principle (SHUR & ZUKAUSKAS, 2005); (b) Emission spectrum (SCHUBERT; GESSMANN & KIM, 2005).                                                                                    | 38 |

| Figure 6  |                                                                                                                                                                                                                                           | 40 |

| Figure 7  | Comparison between the linear and the theoretical models of an LED as well as the points obtained experimentally.(ALMEIDA et al., 2011).                                                                                                  | 40 |

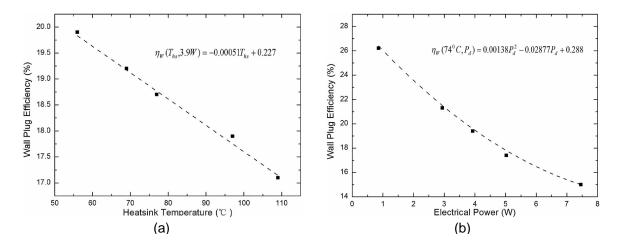

| Figure 8  | Wall-plug efficiency of a Sharp 4.4 W LED according to the heat sink temperature (at constant electrical power - 3.9 W ) (a) and the electrical power (at constant heat sink temperature - 74 $^{\circ}C$ ) (b). (CHEN; TAO & HUI, 2012). | 42 |

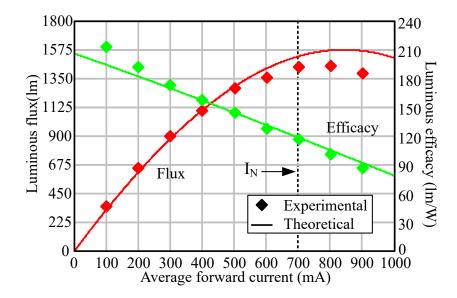

| Figure 9  | Behavior of the luminous flux and the efficacy of an LED Philips Limileds LXML-PWN1 according to variations in the average forward current. (ALMEIDA et al., 2015a)                                                                       | 43 |

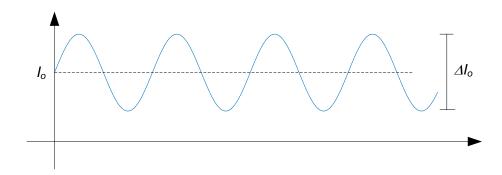

| Figure 10 | Typical current waveform at the LEDs in an off-line application                                                                                                                                                                           | 43 |

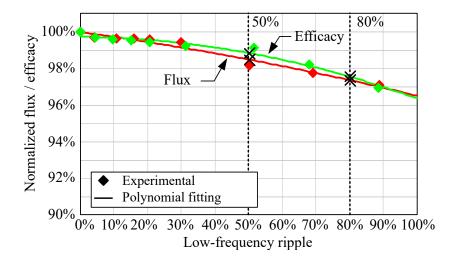

| Figure 11 | Degradation of the luminous flux and the efficacy of a Philips Lumileds LXK2-PWC4 LED string when a Low-frequency Ripple (LFR) is present. (ALMEIDA et al., 2015a).                                                                       | 44 |

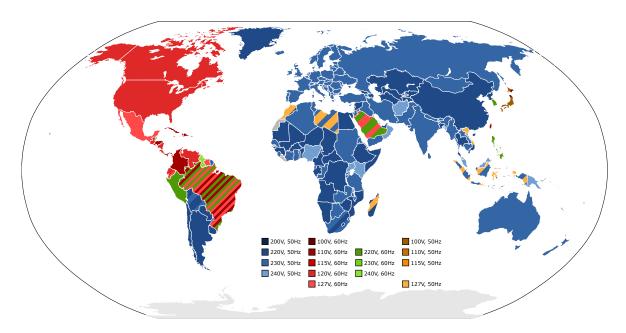

| Figure 12 | Countries of the world, colored according to their domestic nominal power net voltage and frequency. (SOMNUSDE, 2009)                                                                                                                     |    |

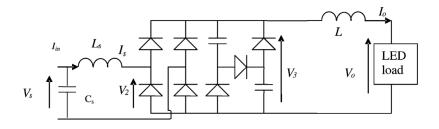

| Figure 13 | Passive LED driver proposed in (HUI et al., 2010).                                                                                                                                                                                        | 52 |

| Figure 14 | Some waveforms of the passive LED driver proposed in (HUI et al.,                                                                                                                                                                         |    |

|           | 2010).(a) Input waveforms: $I_s(\text{CH2} - 0.5\text{A/div})$ , Vs(CH1 - 250V/div) and $I_in(\text{CH2- 0.5A/div})$ ;(b)Output waveforms: $I_o(\text{CH4 - 0.1A/div})$ , $V_3(\text{CH1 - 50V/div})$ .Timescale:4ms.                                                                   | 52 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

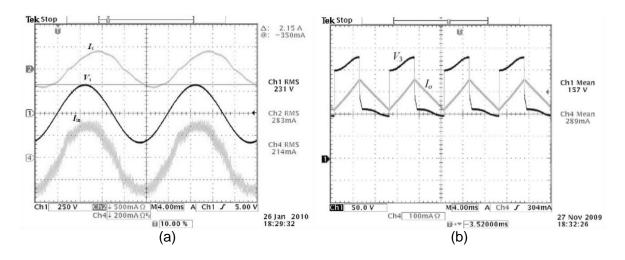

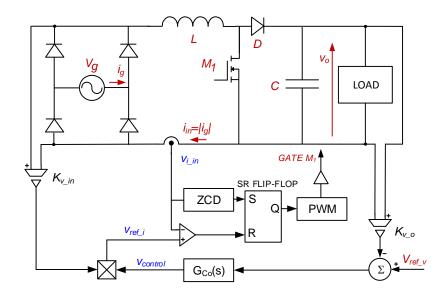

| Figure 15 | Typical schematic of a PFC boost with average current-mode control (CMC).                                                                                                                                                                                                               | 53 |

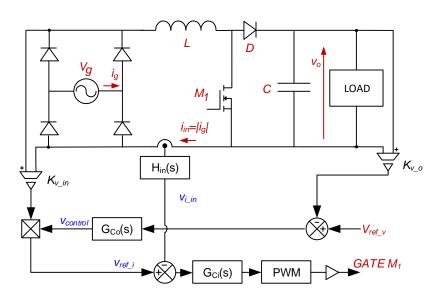

| Figure 16 | Typical schematic of a PFC boost with peak CMC.                                                                                                                                                                                                                                         | 54 |

| Figure 17 | Typical schematic of a Power Factor Correction (PFC) boost operating in Boundary Conduction Modes (BCM) with CMC.                                                                                                                                                                       | 57 |

| Figure 18 | Theoretical waveforms of the BCM boost PFC.                                                                                                                                                                                                                                             | 57 |

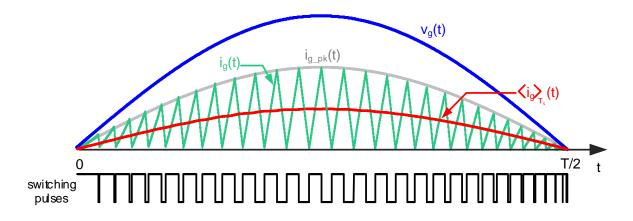

| Figure 19 | Schematics of an LED driver based on a BCM current-controlled SEPIC pre-regulator and linear current equalizers (CHIU et al., 2010)                                                                                                                                                     | 58 |

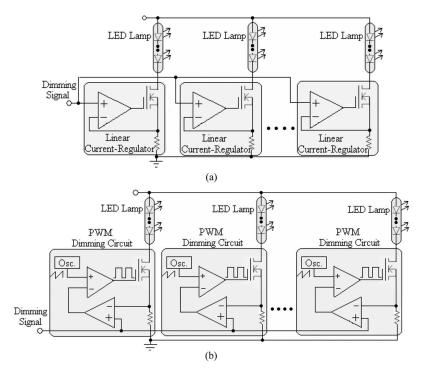

| Figure 20 | Experimental results of the PFC pre-regulator presented in Chiu et al. (2010). Measured input current waveforms at (a) 110V and (b) 220V. (c) Measured input current harmonic.                                                                                                          | 59 |

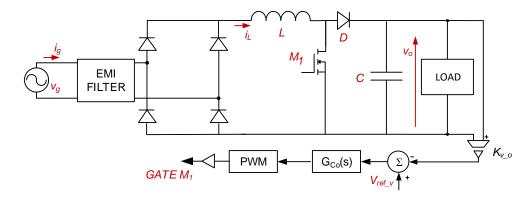

| Figure 21 | voltage-mode control (VMC) boost PFC pre-regulator                                                                                                                                                                                                                                      | 60 |

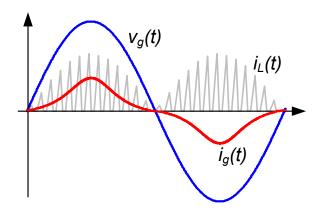

| Figure 22 | Typical waveforms of the boost PFC operating in Discontinuous Conduction Mode (DCM)                                                                                                                                                                                                     | 61 |

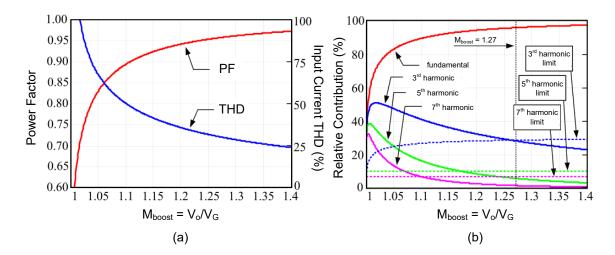

| Figure 23 | Curves of the input parameters of the PFC boost operating in DCM according to variations in the static gain $M_{boost}$ . (a) Curves of power factor (PF) and Total Harmonic Distortion (THD). (b) Curves of the harmonic components of the input current. Adapted from Almeida (2014). | 62 |

| Figure 24 | VMC buck PFC pre-regulator                                                                                                                                                                                                                                                              | 62 |

| Figure 25 | Typical waveforms of the buck PFC operating in DCM                                                                                                                                                                                                                                      | 63 |

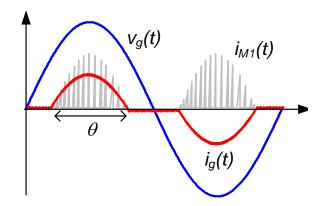

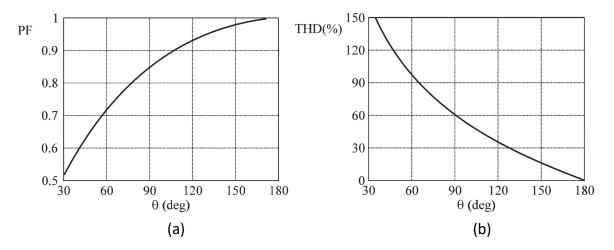

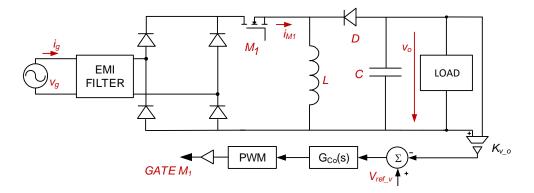

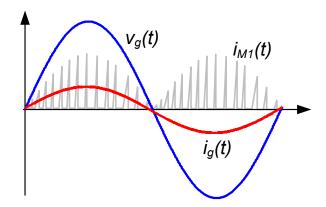

| Figure 26 | Behavior of (a)PF and (b)THD according the conduction angle $\theta$ . (DALLA COSTA et al., 2008)                                                                                                                                                                                       | 64 |

| Figure 27 | VMC buck-boost PFC pre-regulator                                                                                                                                                                                                                                                        | 64 |

| Figure 28 | Typical waveforms of the buck-boost PFC operating in DCM                                                                                                                                                                                                                                | 65 |

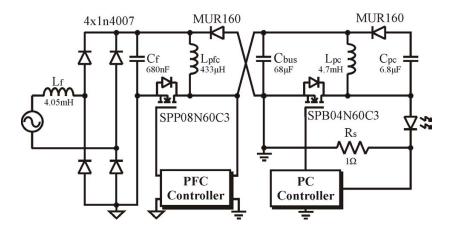

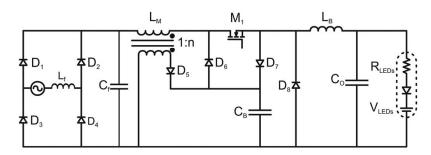

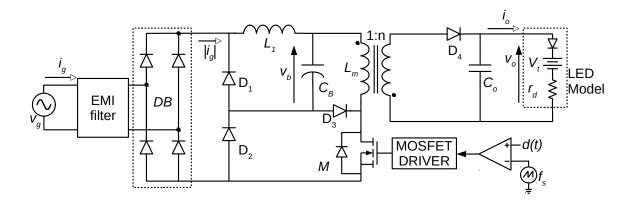

| Figure 29 | Integrated Buck-Flyback Converter presented in Gacio et al. (2015).                                                                                                                                                                                                                     | 66 |

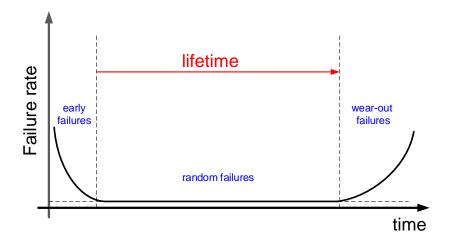

| Figure 30 | Capacitor 's failure rate vs time.                                                                                                                                                                                                                                                      | 69 |

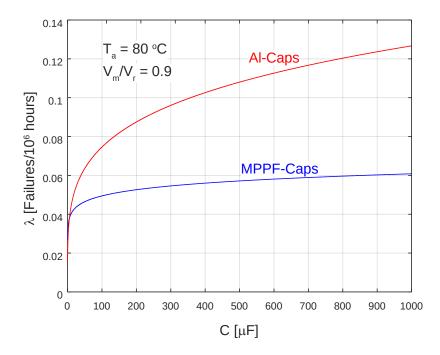

| Figure 31 | Behavior of the FIT as a function of the capacitance for the MPPF-<br>Caps and Al-Caps                                                                                                                                                                                                  | 72 |

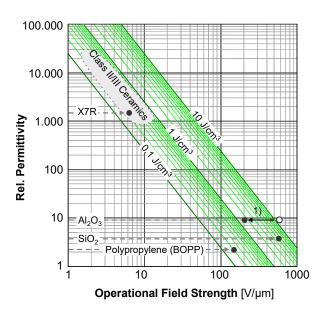

| Figure 32 | Energy storage density according to the dielectric material. März et al. (2010)                                                                                                                                                                                                                     | 72 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

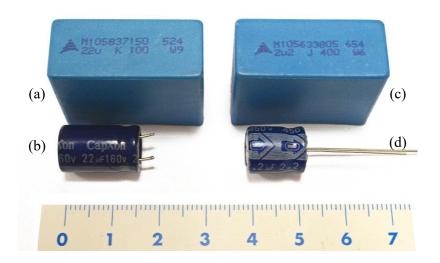

| Figure 33 | Comparison between capacitors with similar nominal values: (a) MPPF-Cap of 22 $\mu$ F and 100 V - 10.5 cm³ (0.0107 J/cm³); b) Al-Cap of 22 $\mu$ F and 160 V - 5.3 cm³ (0.0531 J/cm³); c) MPPF-Cap of 2.2 $\mu$ F and 400 V - 10.5 cm³ (0.0168 J/m³) and d) Al-Cap of 2.2 $\mu$ F e 450 V - 4.1 cm³ |    |

|           | $(0.0543 \text{ J/cm}^3)$ . Ruler in centimeters. (ALMEIDA, 2014)                                                                                                                                                                                                                                   | 73 |

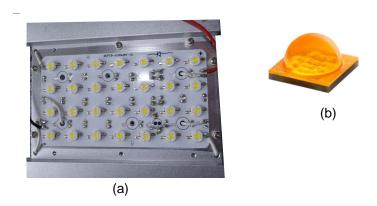

| Figure 34 | (a)LED module composed by 28 devices from Epileds connected in series. (b) Cree high-voltage module CREE XM-L HVW                                                                                                                                                                                   | 75 |

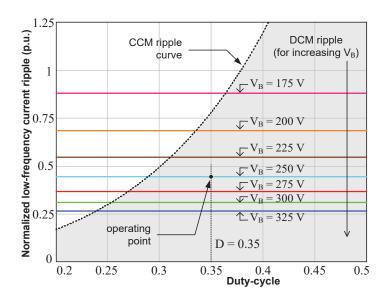

| Figure 35 | Normallized output current ripple of the integrated SEPIC buck-boost converter presented in Almeida, Soares and Braga (2013)                                                                                                                                                                        | 76 |

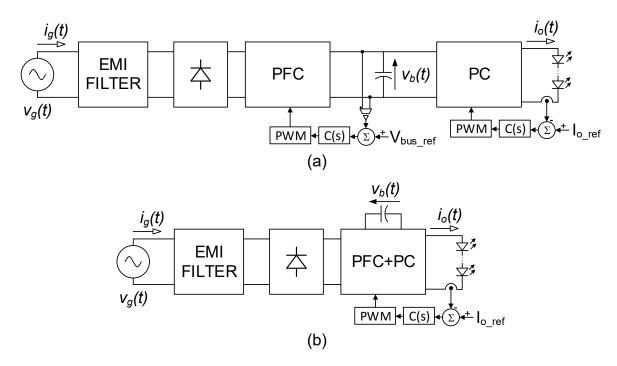

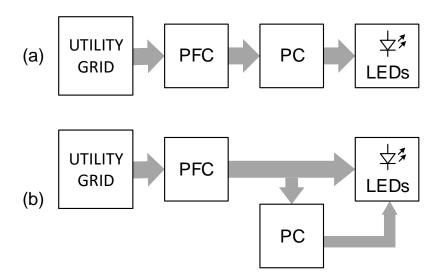

| Figure 36 | Two-stage converters: (a) with independent stages; (b) with integrated stages.                                                                                                                                                                                                                      | 77 |

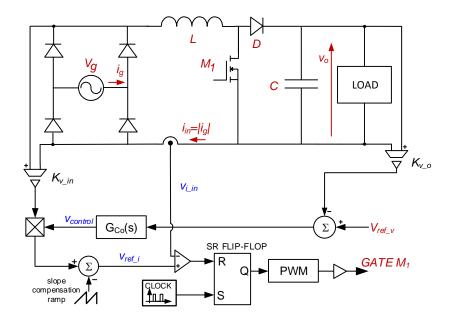

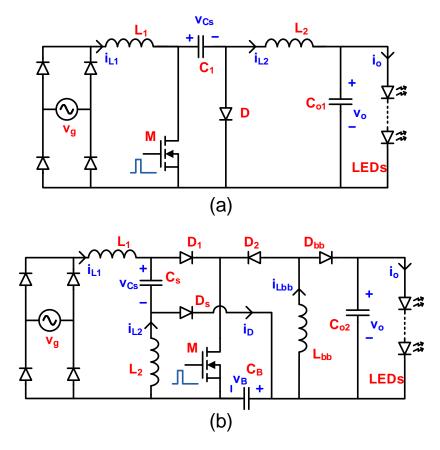

| Figure 37 | Topologies of two off-line LED drivers: (a) Ćuk converter; (b) Integrated                                                                                                                                                                                                                           | 79 |

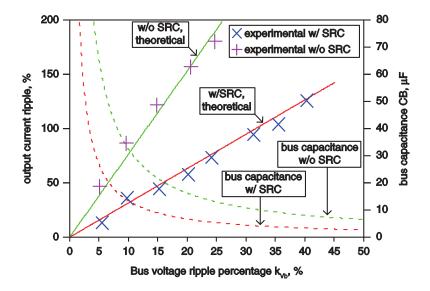

| Figure 38 | Ripple attenuation of a PC SRC. (ALMEIDA et al., 2013)                                                                                                                                                                                                                                              |    |

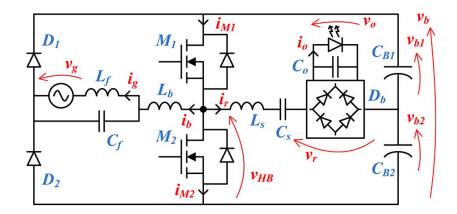

| Figure 39 | Integration between a Bridgeless Boost PFC and an Half-bridge Serie-Resonant Converter for LED driving. (ALMEIDA et al., 2015b)                                                                                                                                                                     |    |

| Figure 40 | Comparison of the energy flow in: (a) a conventional two-stage converter; (b) a two-stage driver with reduced energy processing                                                                                                                                                                     | 81 |

| Figure 41 | Schematics of the converter presented in Camponogara et al. (2013)                                                                                                                                                                                                                                  | 81 |

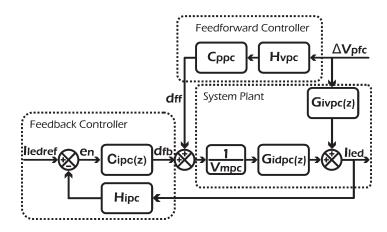

| Figure 42 | Control loop devised for the Power Control (PC) stage presented in Camponogara et al. (2015)                                                                                                                                                                                                        | 81 |

| Figure 43 | Converter proposed in Pereira et al. (2017).                                                                                                                                                                                                                                                        | 82 |

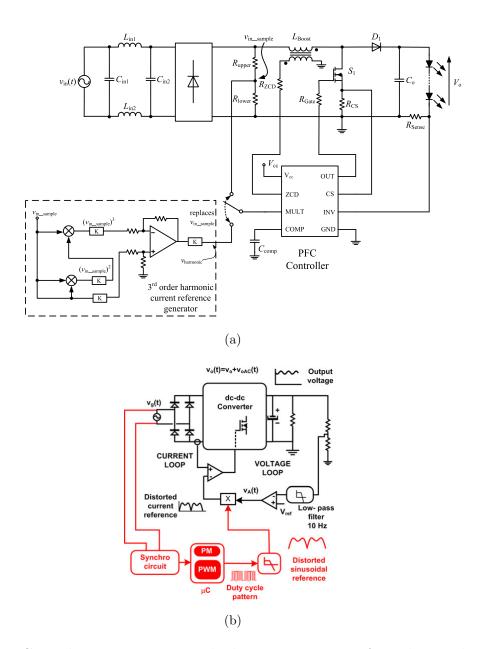

| Figure 44 | Control structures aiming the harmonic injection for reducing the output low-frequency ripple proposed in: (a) Wong et al. (2016); (b) Lamar                                                                                                                                                        |    |

|           | et al. (2012).                                                                                                                                                                                                                                                                                      | 84 |

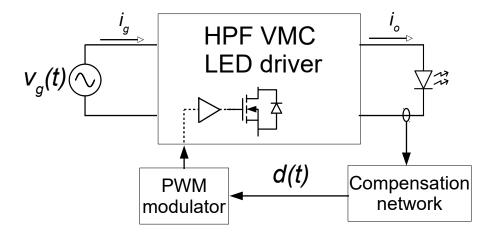

| Figure 45 | Basic diagram of a voltage-mode controlled LED driver                                                                                                                                                                                                                                               | 86 |

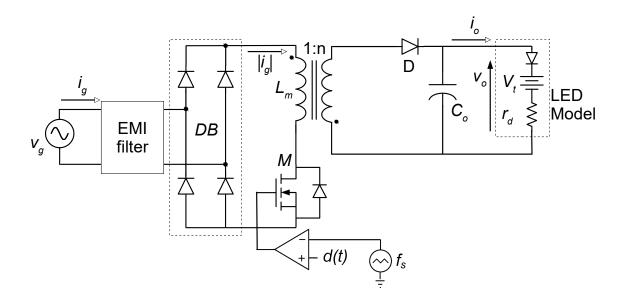

| Figure 46 | Basic diagram of an off-line flyback LED driver.                                                                                                                                                                                                                                                    | 87 |

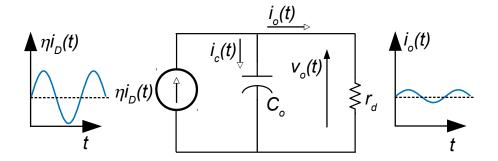

| Figure 47 | Low-frequency equivalent model of the flyback converter output                                                                                                                                                                                                                                      | 90 |

| Figure 48 | MATLAB pseudo-code for calculating the output current of the flyback-                                                                                                                                                                                                                               |    |

|           | based LED driver. 91                                                                                                                                                                                                                                                                      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

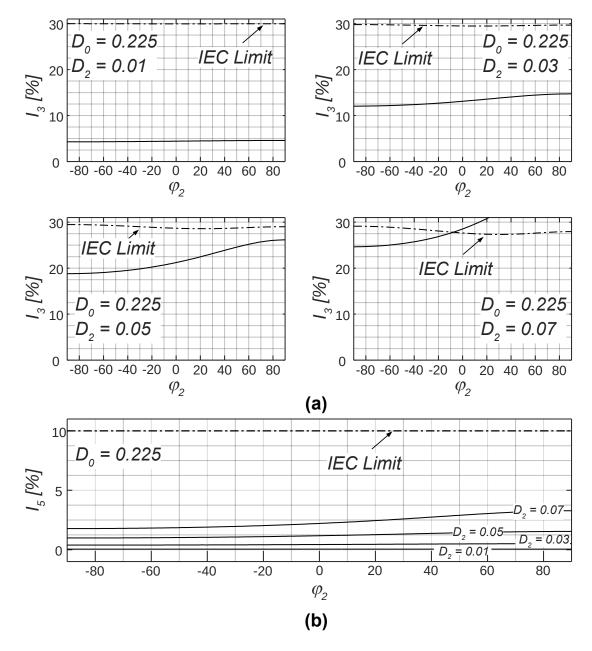

| Figure 49 | Behavior of the input current according to variations on the duty cycle parameters: (a) third harmonic component; (b) fifth harmonic compo-                                                                                                                                               |

|           | nent 94                                                                                                                                                                                                                                                                                   |

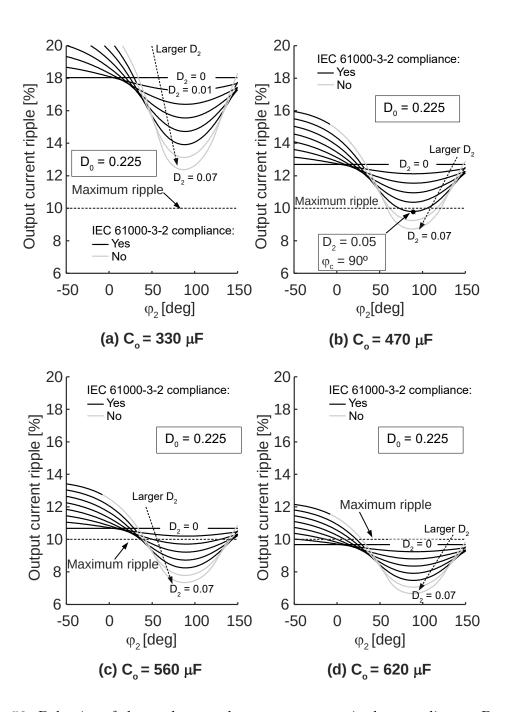

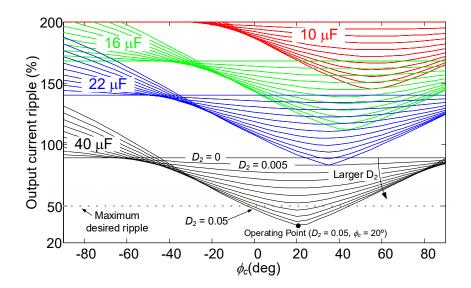

| Figure 50 | Behavior of the peak-to-peak output current ripple according to $D_2$ and $\phi_2$ for several values of $C_o$ . 96                                                                                                                                                                       |

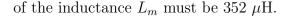

| Figure 51 | Variation of the magnetizing inductance according to the duty cycle                                                                                                                                                                                                                       |

|           | parameters 97                                                                                                                                                                                                                                                                             |

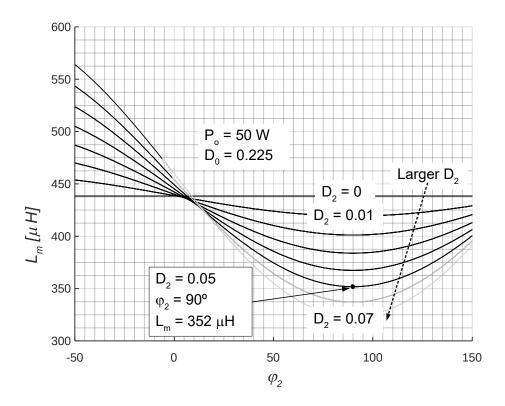

| Figure 52 | Diagram of the proposed closed-loop system 98                                                                                                                                                                                                                                             |

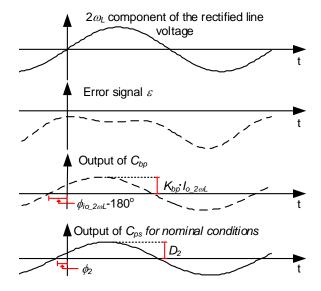

| Figure 53 | Theoretical waveforms of the ARC branch of the control structure 99                                                                                                                                                                                                                       |

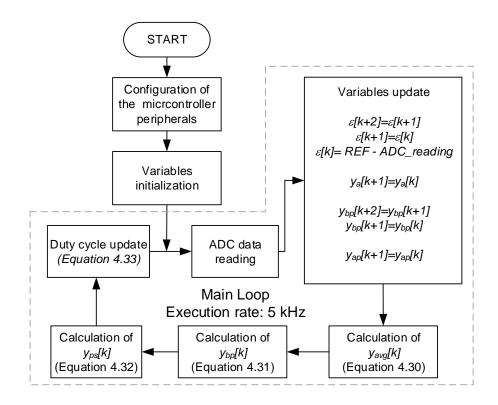

| Figure 54 | Flowchart of the control algorithm                                                                                                                                                                                                                                                        |

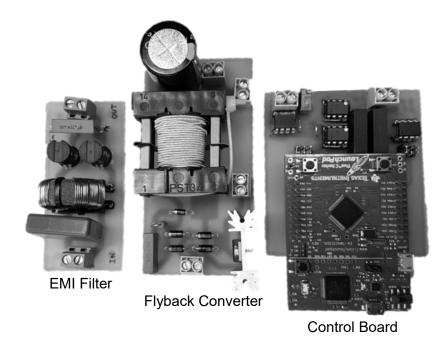

| Figure 55 | Photograph of the prototype                                                                                                                                                                                                                                                               |

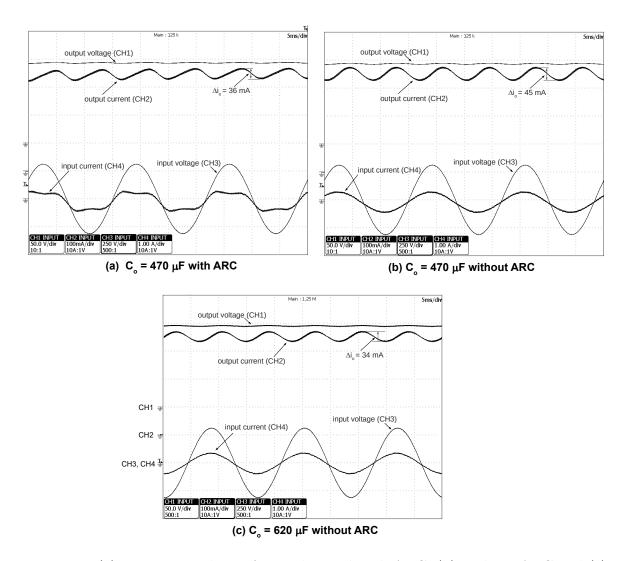

| Figure 56 | (a) Experimental waveforms obtained with ARC, (b) without ARC and (c) results without ARC with $C_o=620~\mu F$ . Output voltage (CH1 - $50V/div$ ), output current(CH2 - $100~mA/div$ ), input voltage (CH3 - $250V/div$ ) and input current ( $1A/div$ ). Horiz. scale: $5~ms/div$ $105$ |

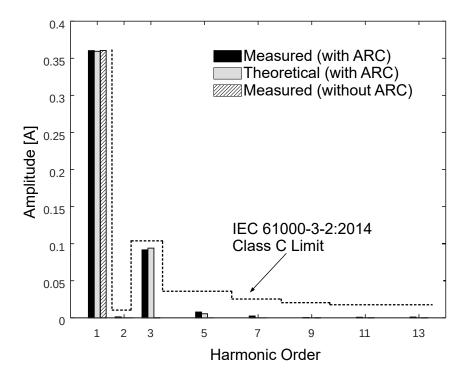

| Figure 57 | Harmonic content of the input current                                                                                                                                                                                                                                                     |

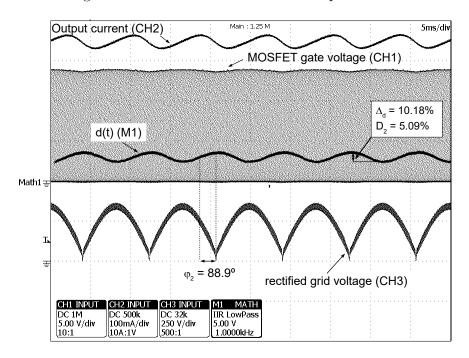

| Figure 58 | Behavior of the duty cycle in steady-state. MOSFET gate voltage (CH1 - 5V/div); duty cycle (M1 - IIR Lowpass filter with a cut-off frequency of 1 kHz - 5V/div) output current (CH2 - 100 mA/div); rectified grid voltage (CH3 - 250 V/div). Horizontal scale: 5 ms/div                   |

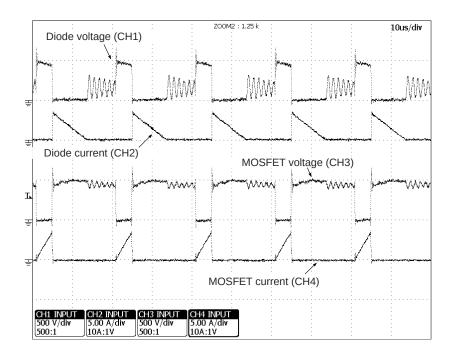

| Figure 59 | MOSFET voltage (CH3 - 500 V/div) and current (CH4 - 5A/div). Diode $D$ voltage (CH1 - 500 V/div) and current (CH2 - 5A/div). Waveforms measured at the peak of the rectified voltage. Horiz. scale: 10 $\mu$ s/div                                                                        |

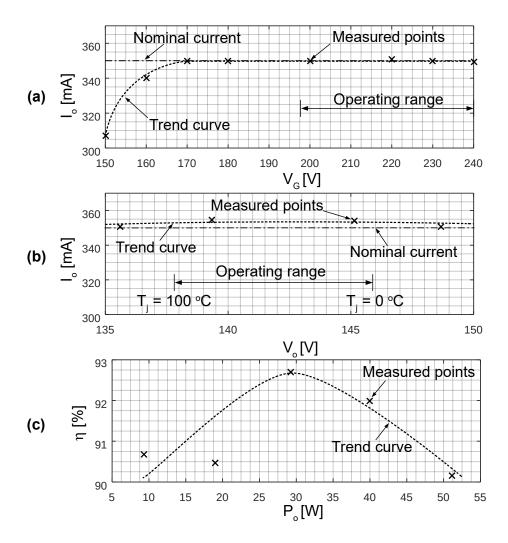

| Figure 60 | Behavior of the converter owing to variations of the input voltage and the load. (a) Output current regulation for input voltage variations; (b) Output current regulation for output voltage variations; (c) Efficiency of the converter for several load levels (dimming)               |

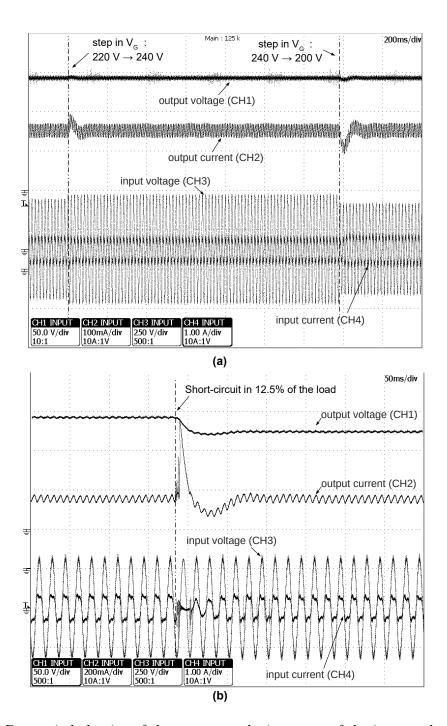

| Figure 61 | Dynamic behavior of the converter during steps of the input voltage (a) and the load(b). Output voltage (CH1: 50V/div), output current(CH2: 100 mA/div in (a) - 200 mA/div in(b)), input voltage (CH3: 250V/div) and input current (1A/div). Horiz. scale: 200 ms/div in (a) and 50       |

|           | ms/div in (b)                                                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

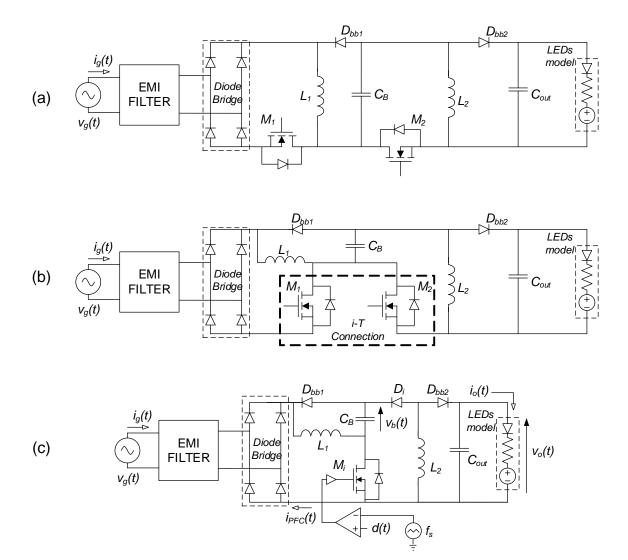

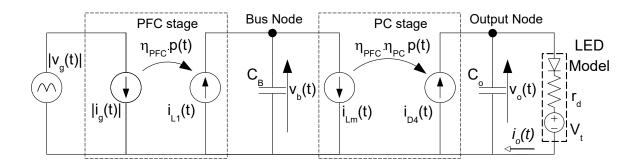

| Figure 62 | Two-stage converter based on the cascade connection of two buck-boost topologies. (a) independent stages; (b) i-T connection; (a) Integrated Double Buck-Boost (IDBB) converter                                                                                                                        |

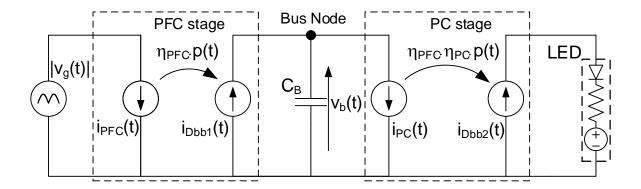

| Figure 63 | Large-signal low-frequency model of the IDBB converter                                                                                                                                                                                                                                                 |

| Figure 64 | MATLAB pseudo-code for calculating the output current of the IDBB converter                                                                                                                                                                                                                            |

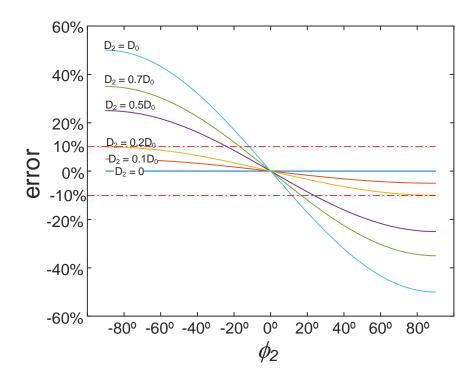

| Figure 65 | Relative error of the IDBB converter input power with ARCT considering only the average value of the duty cycle                                                                                                                                                                                        |

| Figure 66 | Harmonic content of the input current according to the oscillating component of the duty-cycle: (a) third harmonic component.; (b) fifth harmonic component                                                                                                                                            |

| Figure 67 | Behavior of the peak-to-peak output current ripple according to the ARC parameters for several values of $C_B$                                                                                                                                                                                         |

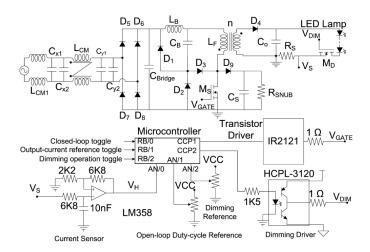

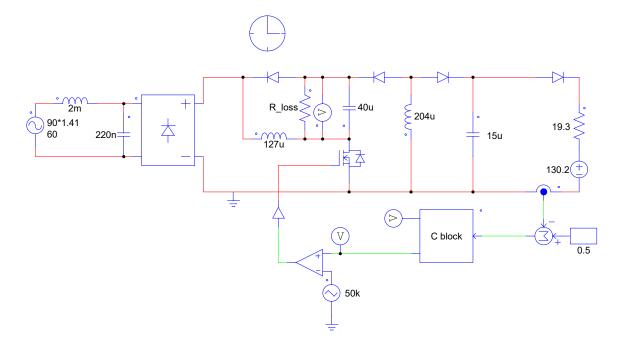

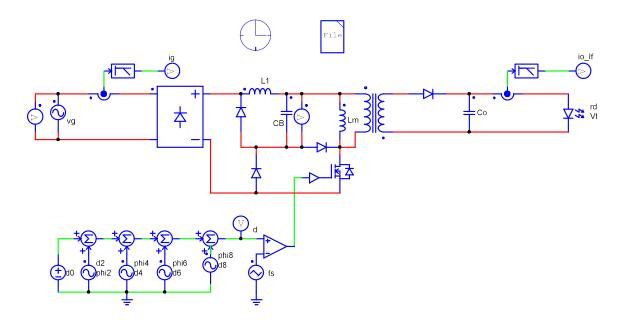

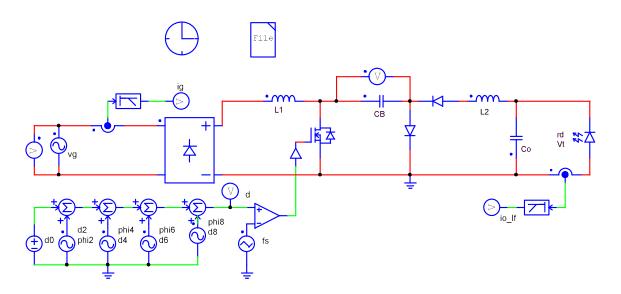

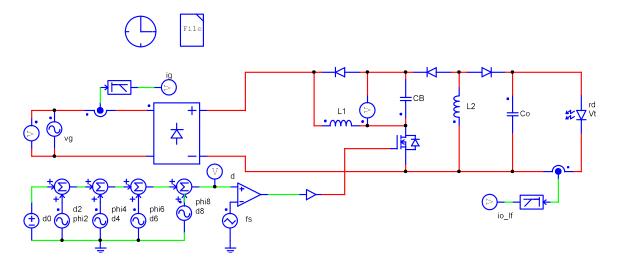

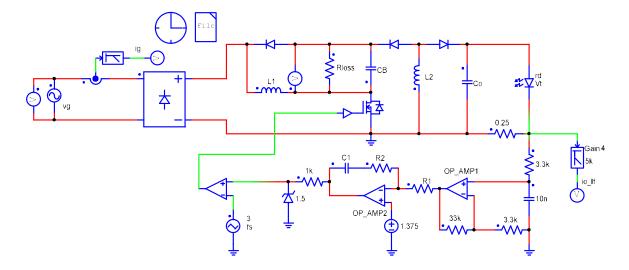

| Figure 68 | Circuit used in the simulation of the IDBB converter with ARCT121                                                                                                                                                                                                                                      |

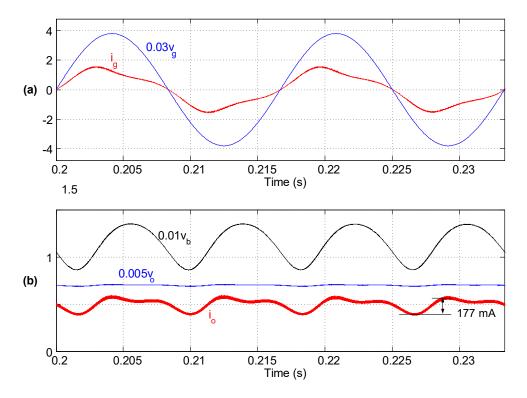

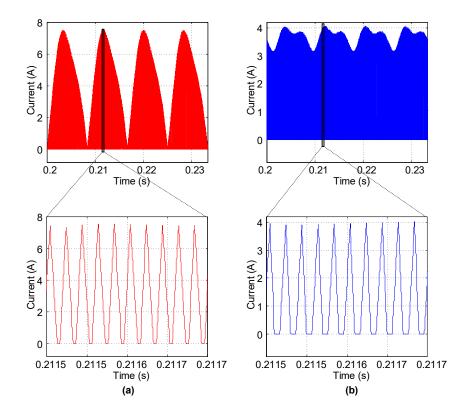

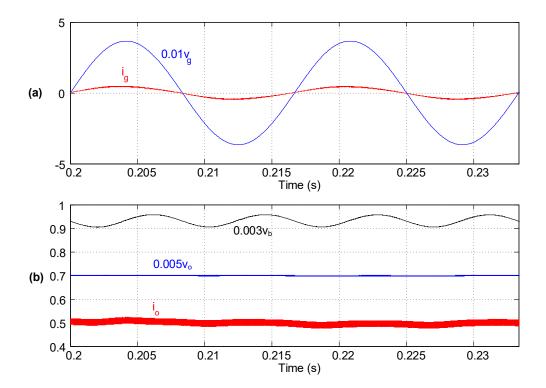

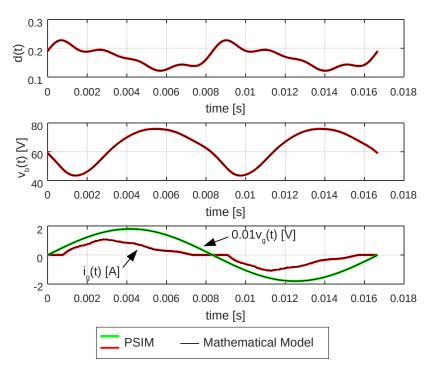

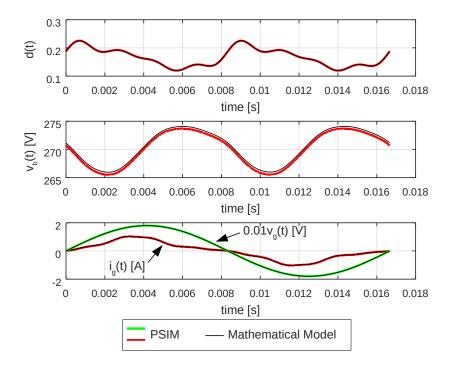

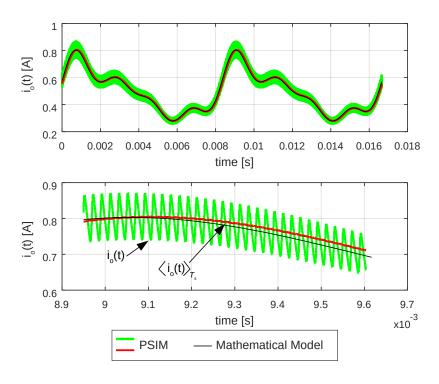

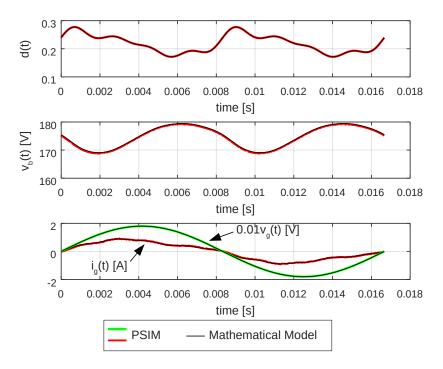

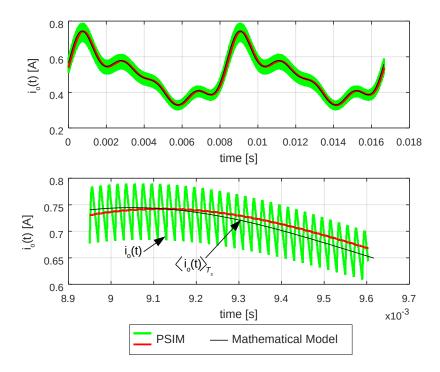

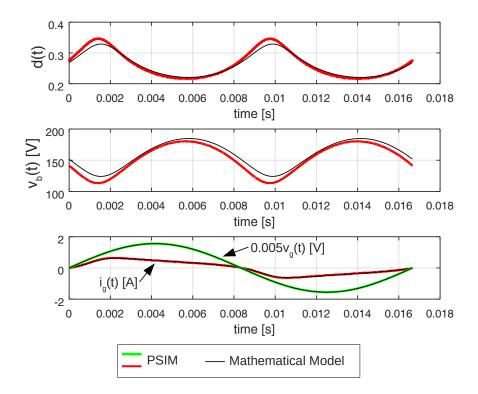

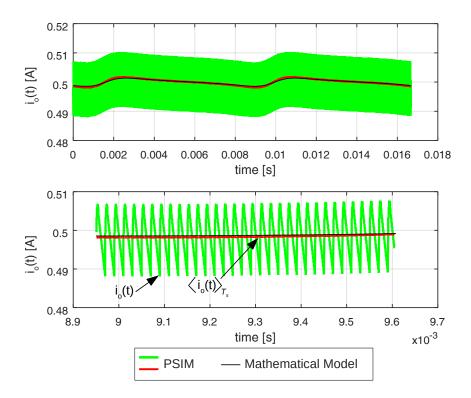

| Figure 69 | Simulation results for $V_G = \sqrt{2} \cdot 90  V$ . (a) Input variables; (b) bus voltage and output variables                                                                                                                                                                                        |

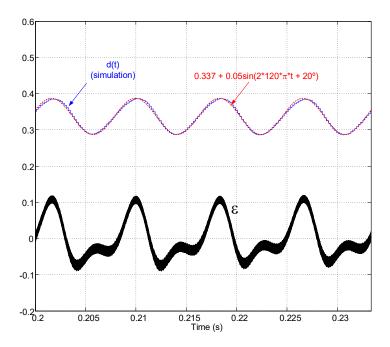

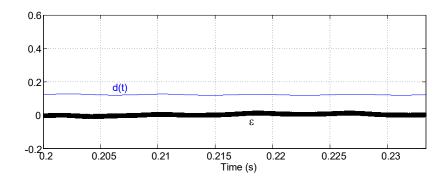

| Figure 70 | Simulation of the signal $d(t)$ and the error signal $\epsilon$                                                                                                                                                                                                                                        |

| Figure 71 | Simulation of the low-frequency and high-frequency behavior of the inductors's current: (a)Inductor $L_1$ ; (a)Inductor $L_2$                                                                                                                                                                          |

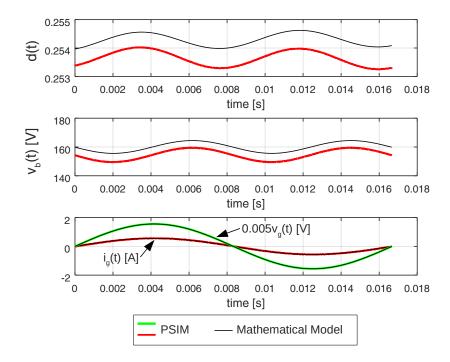

| Figure 72 | Simulation results for $V_G = \sqrt{2} \cdot 260V$ . (a) Input variables; (b) bus voltage and output variables                                                                                                                                                                                         |

| Figure 73 | Simulation of the signal $d(t)$ and the error signal $\epsilon$ for $V_G = \sqrt{2} \cdot 260V$ . 125                                                                                                                                                                                                  |

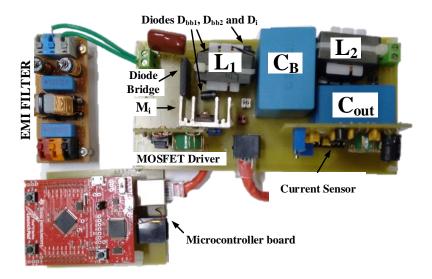

| Figure 74 | Top-view of the complete prototype, showing both power and digital control circuitry, along with the MOSFET driver and current sensor boards (mounted vertically)                                                                                                                                      |

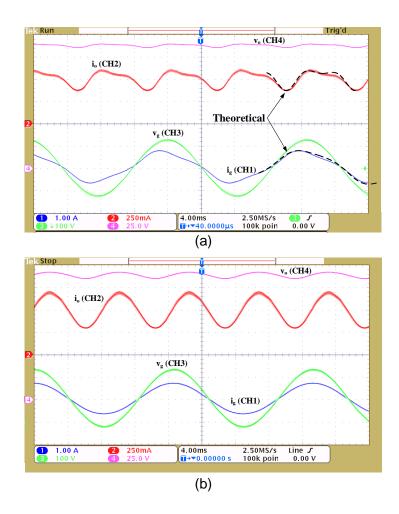

| Figure 75 | Experimental waveforms obtained with Active Ripple-Compensation Technique (ARCT) (a) and without ARCT (b) for an input voltage of 90 V RMS. Input current (CH1 - 1A/div), output current (CH2 - 250 mA/div), mains voltage (CH3 - 100/div) and output voltage (CH4 - 25 V/div). Horiz. Scale: 4 ms/div |

| Figure 76 | Experimental waveforms obtained for an input voltage of 260 V RMS. Input current (CH1 - 1 A/div), output current (CH2 - 250 mA/div),                                                                                                                                                                   |

|           | mains voltage (CH3 - 250/div) and output voltage (CH4 - 25 V/div).  Horiz. Scale: 4 ms/div                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

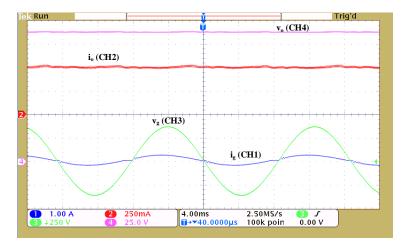

| Figure 77 | Efficiency of the converter. (a) Behavior for variations of the input voltage at full-load;(b) behavior for variations of the output load with $V_G = \sqrt{2} \cdot 115  V$                                            |

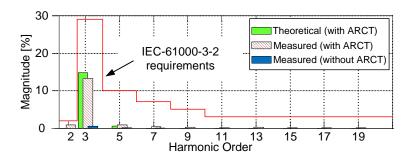

| Figure 78 | Harmonic content of the input current compared to the limits imposed by the IEC-61000-3-2:2014 standard (class C equipment). $V_G = \sqrt{2} \cdot 90$ V                                                                |

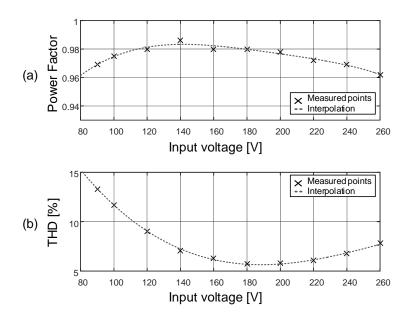

| Figure 79 | Variation of the power factor (a) and THD (b) with the line voltage. 129                                                                                                                                                |

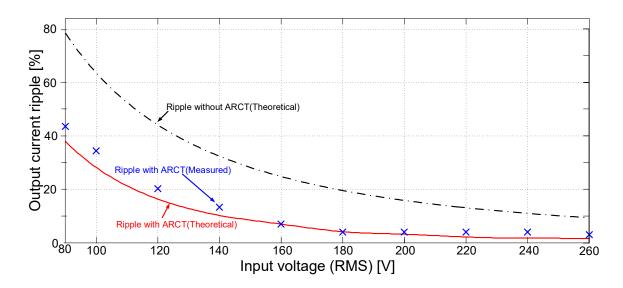

| Figure 80 | Behavior of the output current ripple for variations in the mains voltage magnitude                                                                                                                                     |

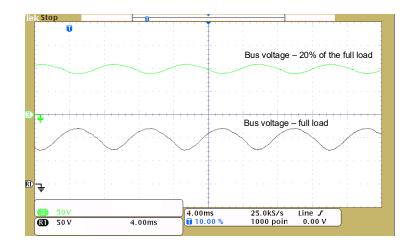

| Figure 81 | Behavior of the bus voltage according to load variations for an input voltage of 90 V. Bus voltage for 20% of the full load (CH3 - 50 V/div); Bus voltage for full load (R1 - 50 V/ div). Time scale: 4 ms. $\dots 131$ |

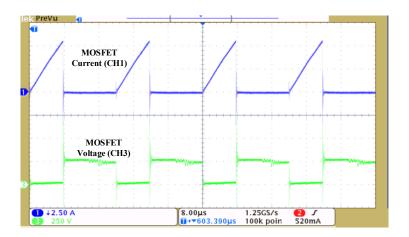

| Figure 82 | Current (CH1, 2.5 A/div) and voltage (CH3, 250 V/div) measured at the MOSFET in the peak of the rectified voltage. Time scale: $8\mu$ s/div. 131                                                                        |

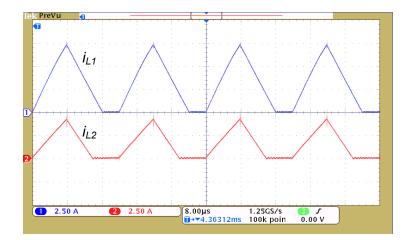

| Figure 83 | High frequency behavior of the current of the inductors $L_1$ (CH1, 2.5 A/div) and $L_2$ (CH2, 2.5 A/div) measured at the peak of the rectified voltage ( $V_G = \sqrt{2} \cdot 90$ ). Time scale: 8 $\mu$ s/div        |

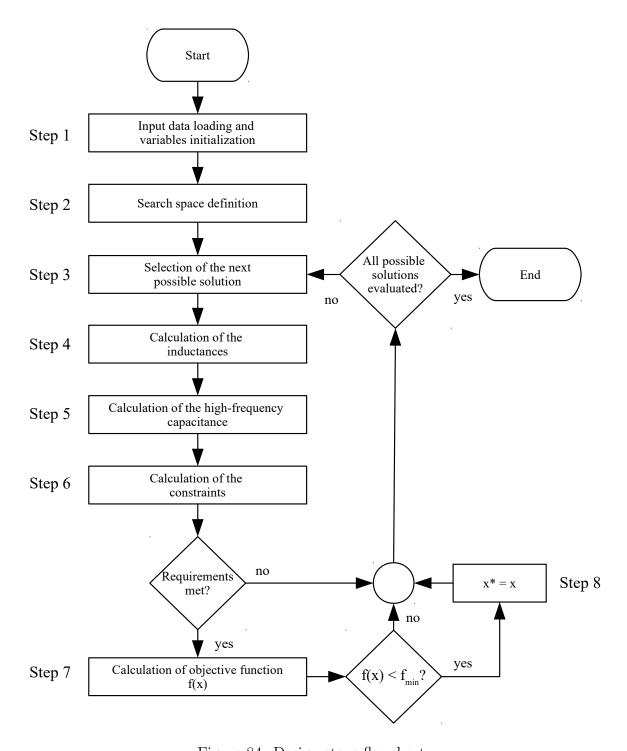

| Figure 84 | Design steps flowchart. 138                                                                                                                                                                                             |

| Figure 85 | Circuit used in the simulation of the flyback converter                                                                                                                                                                 |

| Figure 86 | Comparison between the simulated waveforms with the theoretical model of the flyback converter                                                                                                                          |

| Figure 87 | Integrated Buck Flyback Converter                                                                                                                                                                                       |

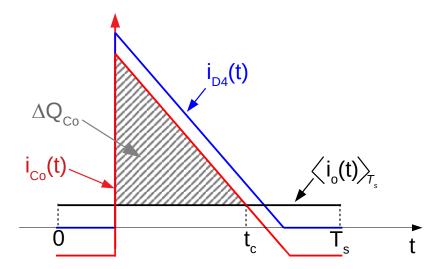

| Figure 88 | Theoretical high-frequency current waveforms in the output node of the IBuFly converter                                                                                                                                 |

| Figure 89 | Large-signal low-frequency model of the IBuFly converter                                                                                                                                                                |

| Figure 90 | Circuit used in the simulation of the IBuFly converter                                                                                                                                                                  |

| Figure 91 | Comparison between the simulated waveforms with the theoretical model of the IBuFly converter                                                                                                                           |

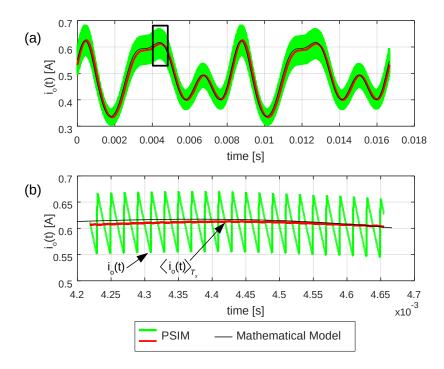

| Figure 92 | Comparison between the simulated waveforms of the IBuFly converter output current with the theoretical model. (a) Low-frequency behavior; (b) High-frequency waveforms                                                  |

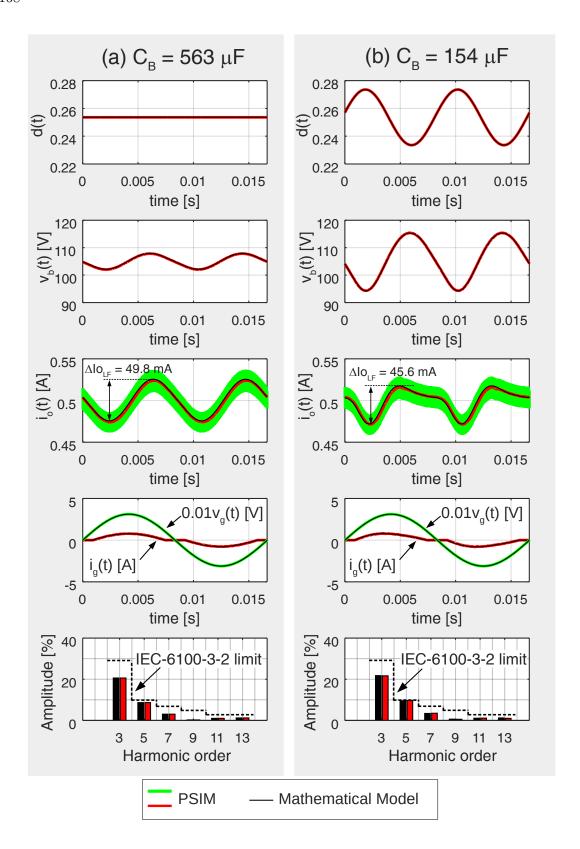

| Figure 93                                                                               | Comparison between the simulated waveforms with the theoretical model of the IBuFly converter for the case no. 15. (a) Default de-                                                                                                                                      |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         | sign ( $C_B=563~\mu F$ - without ARC). (b) Optimized design ( $C_B=154~\mu F$ - ARC with the 2nd harmonic)                                                                                                                                                              |

| Figure 94                                                                               | Integrated Boost Buck Converter                                                                                                                                                                                                                                         |

| Figure 95                                                                               | Circuit used in the simulation of the IBoBu converter                                                                                                                                                                                                                   |

| Figure 96                                                                               | Comparison between the simulated waveforms with the theoretical model of the IBoBu converter                                                                                                                                                                            |

| Figure 97                                                                               | Comparison between the simulated waveforms of the IBoBu converter output current with the theoretical model. (a) Low-frequency behavior; (b) High-frequency waveforms                                                                                                   |

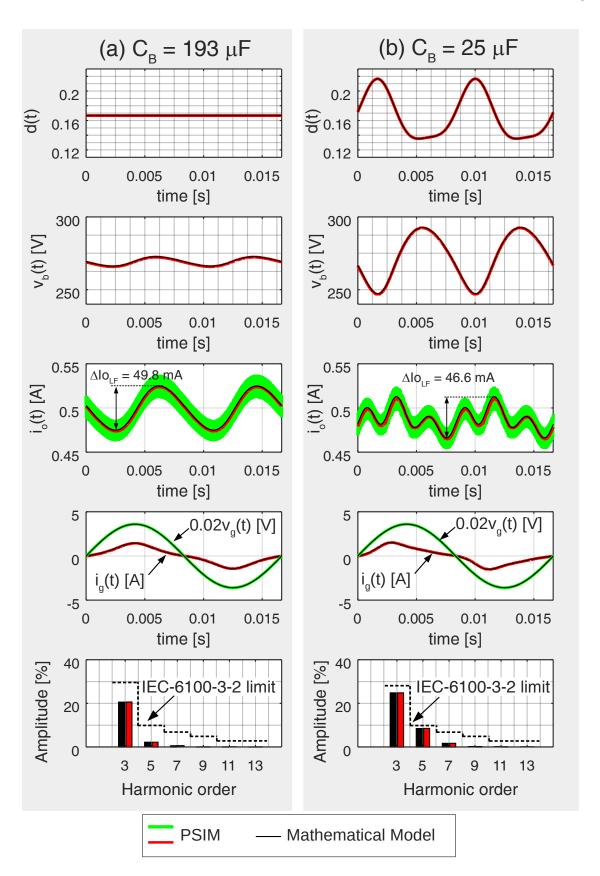

| Figure 98                                                                               | Comparison between the simulated waveforms with the theoretical model of the IBoBu converter for the case no. 3. (a) Default design $(C_B=193~\mu F$ - without ARC). (b) Optimized design $(C_B=25~\mu F$ - ARC with the 2 <sup>nd</sup> and 4 <sup>th</sup> harmonics) |

| Figure 99                                                                               | Circuit used in the simulation of the IDBB converter                                                                                                                                                                                                                    |

|                                                                                         |                                                                                                                                                                                                                                                                         |

| Figure 100                                                                              | Comparison between the simulated waveforms with the theoretical model of the IDBB converter                                                                                                                                                                             |

|                                                                                         | -                                                                                                                                                                                                                                                                       |

| Figure 101                                                                              | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102                                                                   | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102 Figure 103                                                        | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102 Figure 103 Figure 104                                             | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102 Figure 103 Figure 104 Figure 105                                  | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102 Figure 103 Figure 104 Figure 105 Figure 106                       | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102 Figure 103 Figure 104 Figure 105 Figure 106 Figure 107            | model of the IDBB converter                                                                                                                                                                                                                                             |

| Figure 101 Figure 102 Figure 103 Figure 104 Figure 105 Figure 106 Figure 107 Figure 108 | model of the IDBB converter                                                                                                                                                                                                                                             |

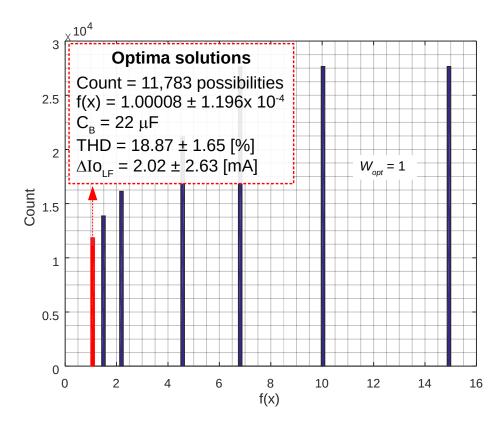

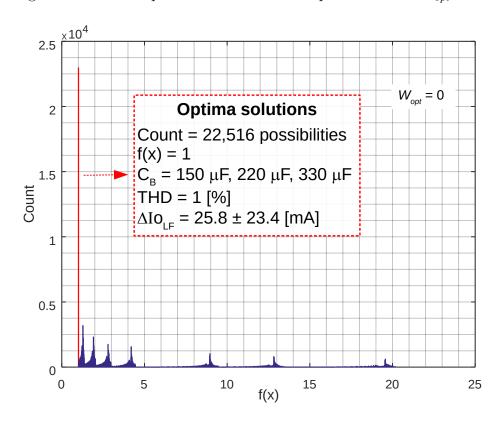

| Figure 110 | Histogram of the objective function for $w_{opt} = 0$                                                                                                                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

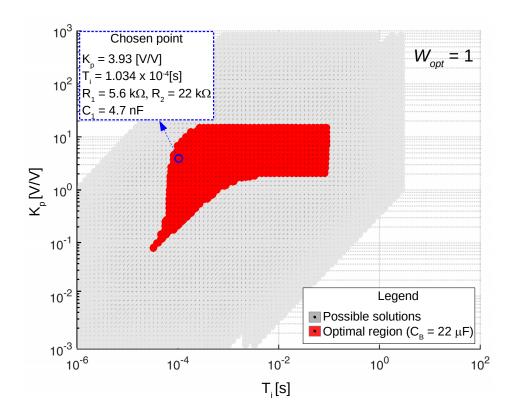

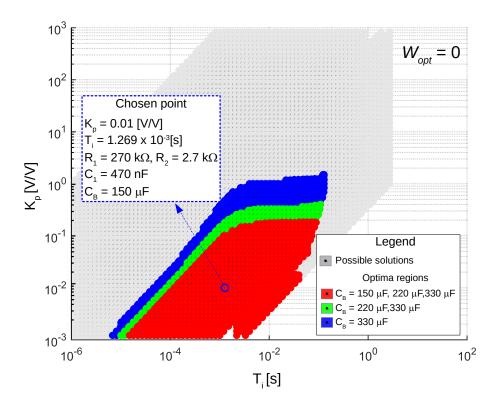

| Figure 111 | Scatter plot of the PI controller parameters for $w_{opt} = 0$                                                                                                                                                                                                                                                                       |

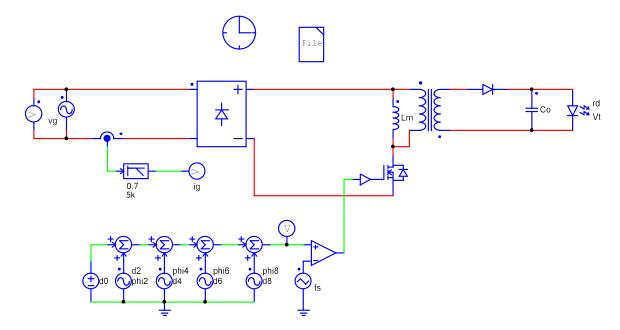

| Figure 112 | Circuit used in the simulation of the IDBB converter with an analog PI controller                                                                                                                                                                                                                                                    |

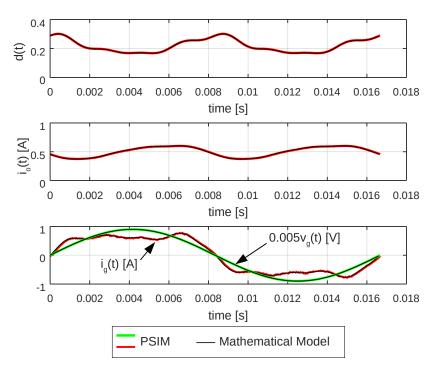

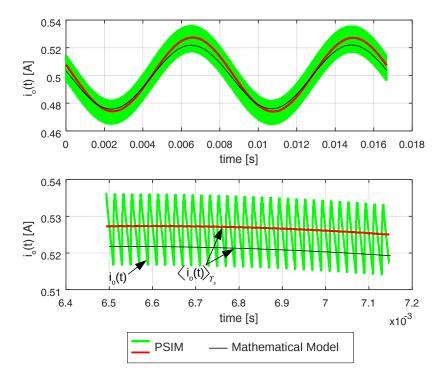

| Figure 113 | Comparison between the simulated waveforms with the theoretical model of the IDBB converter for $w_{opt} = 1$                                                                                                                                                                                                                        |

| Figure 114 | Comparison between the simulated waveforms of the IDBB converter output current with the theoretical model for $w_{opt}=1$ . (a) Lowfrequency behavior; (b) High-frequency waveforms                                                                                                                                                 |

| Figure 115 | Comparison between the simulated waveforms with the theoretical model of the IDBB converter for $w_{opt} = 0$                                                                                                                                                                                                                        |

| Figure 116 | Comparison between the simulated waveforms of the IDBB converter output current with the theoretical model for $w_{opt} = 0$ . (a) Low-frequency behavior; (b) High-frequency waveforms                                                                                                                                              |

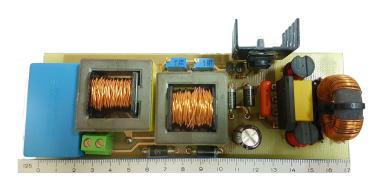

| Figure 117 | Top-view of the prototype with $C_B=22~\mu\mathrm{F}.$ Ruler in centimeters 221                                                                                                                                                                                                                                                      |

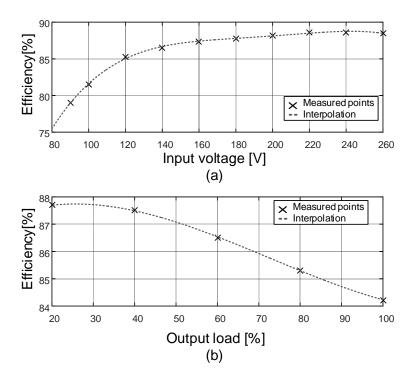

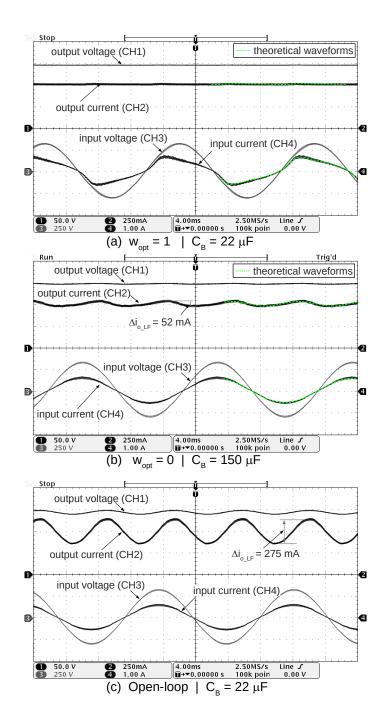

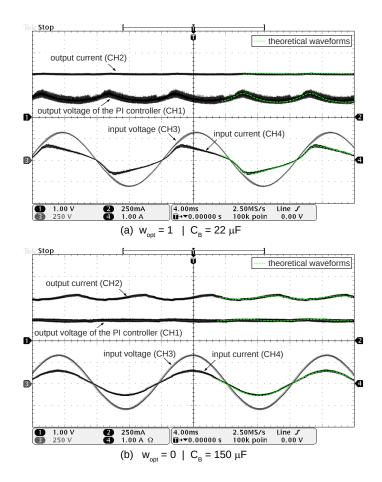

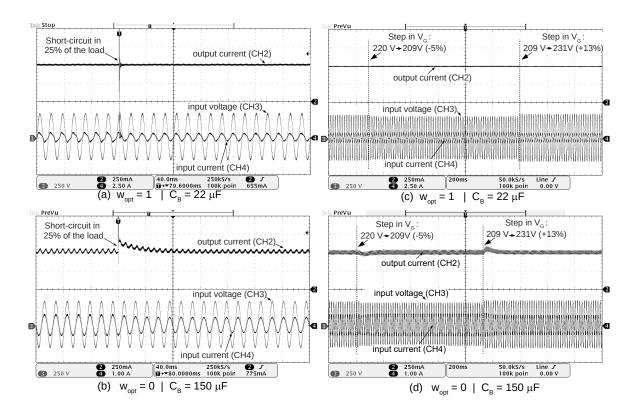

| Figure 118 | Experimental waveforms obtained for the design with $w_{opt}=1(a)$ and $w_{opt}=0$ (b). (c) Results obtained for the circuit operating in open-loop with $C_B=22~\mu {\rm F}$ . Output voltage (CH1 - 50V/div), output current(CH2 - 250 mA/div), input voltage (CH3 - 250V/div) and input current (1A/div). Horiz. scale: 4 ms/div. |

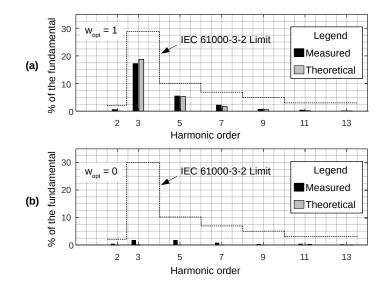

| Figure 119 | Harmonic content of the input current for $w_{opt} = 1(a)$ and $w_{opt} = 0(b)$                                                                                                                                                                                                                                                      |

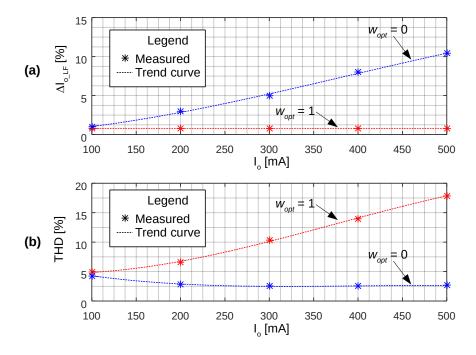

| Figure 120 | Behavior of the output current ripple (a) and the THD of the input current (b) for variations in the output power                                                                                                                                                                                                                    |

| Figure 121 | Behavior of the duty cycle in steady-state for $w_{opt} = 1(a)$ and $w_{opt} = 0(b)$ . Output voltage of the PI controller(CH1 - 1V/div), output current(CH2 - 250 mA/div), input voltage (CH3 - 250V/div) and input current (1A/div). Horiz. scale: 4 ms/div                                                                        |

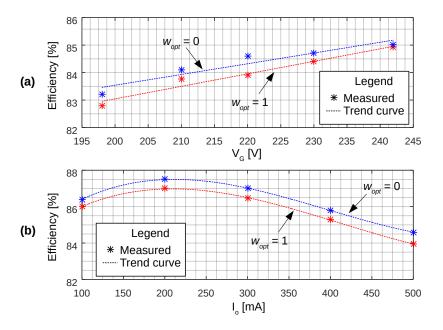

| Figure 122 | Efficiency of the converter according to variations in the input voltage (a) and the output current (b). Data taken with $V_G = 220 \text{ V.} \dots 225$                                                                                                                                                                            |

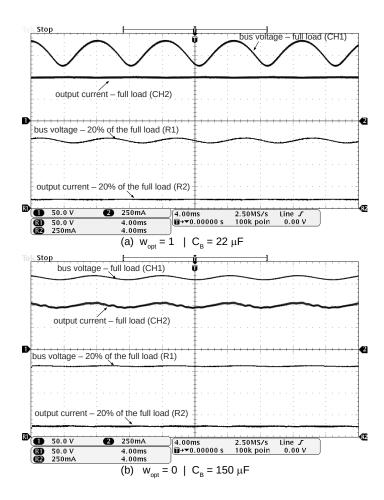

| Figure 123 | Behavior of the bus voltage according to load variations for an input voltage of 220 V. Bus voltage for full load (CH1 - $50 \text{ V/div}$ ); Bus voltage                                                                                                                                                                           |

|            | for 20% of the full load (R1 - 50 V/ div); Output current for full load                                   |

|------------|-----------------------------------------------------------------------------------------------------------|

|            | (CH2 - 250 mA/div); Output current for 20% of the full load (R2 - 250                                     |

|            | mA/div). Time scale: 4 ms. $000000000000000000000000000000000000$                                         |

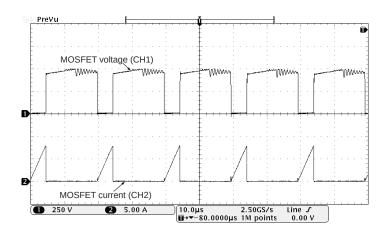

| Figure 124 | MOSFET voltage (CH1 - 250 V/div) and current (CH2 - 5A/div).                                              |

|            | Horiz. scale: 10 $\mu s/div$                                                                              |

| Figure 125 | Dynamic behavior of the converter during steps of the input voltage (a)                                   |

|            | and the load(b). Output voltage (CH1: $50V/div$ ), output current(CH2:                                    |

|            | $100~\mathrm{mA/div}$ in (a) - $200~\mathrm{mA/div}$ in<br>(b)), input voltage (CH3: $250\mathrm{V/div})$ |

|            | and input current (1A/div). Horiz. scale: $200 \text{ ms/div}$ in (a) and $50 \text{ ms/div}$             |

|            | ms/div in (b)                                                                                             |

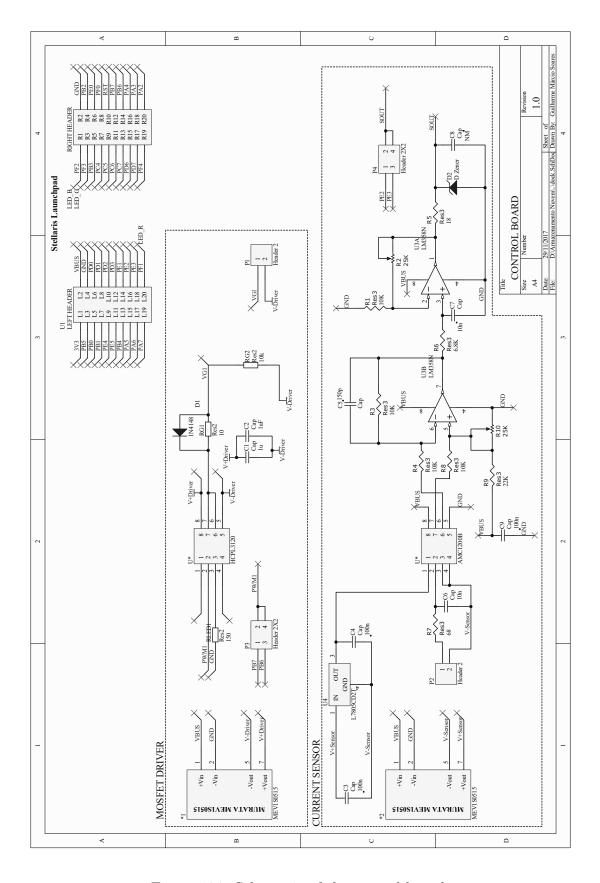

| Figure 126 | Schematic of the control board                                                                            |

| Figure 127 | C-block - Variable/Function definitions                                                                   |

| Figure 128 | C-block - Implementation of the RunSimUser Fcn247                                                         |

|            |                                                                                                           |

## LIST OF TABLES

| Table 1  | Limits of harmonic emission of Class C equipment according to the IEC-61000-3-2:2014.                          | 50  |

|----------|----------------------------------------------------------------------------------------------------------------|-----|

| Table 2  | Comparison of two capacitors from Panasonic with a different relation-<br>ship between capacitance and voltage | 74  |

| Table 3  | Design Parameters                                                                                              | 92  |

| Table 4  | Control circuit parameters                                                                                     | 101 |

| Table 5  | Coefficients used in the discrete implementation                                                               | 102 |

| Table 6  | Main Prototype Components                                                                                      | 103 |

| Table 7  | Measured Loss Distribution                                                                                     | 105 |

| Table 8  | Parameters for the design of the IDBB converter                                                                | 115 |

| Table 9  | Control circuit parameters                                                                                     | 120 |

| Table 10 | Coefficients used in the discrete implementation                                                               | 121 |

| Table 11 | Prototype parameters                                                                                           | 125 |

| Table 12 | Values used in the simulation of the flyback converter                                                         | 142 |

| Table 13 | Simulation results of the flyback converter.                                                                   | 143 |

| Table 14 | Specification of the PPEE-UFJF cluster                                                                         | 144 |

| Table 15 | Cases studied in the flyback converter                                                                         | 145 |

| Table 16 | Range of the optimization variables.                                                                           | 146 |

| Table 17 | Estimation of the time spent for solving the optimization routine                                              | 146 |

| Table 18 | Output capacitance and $\Delta C_{\%}$ of the flyback converter with ARC for all the studied cases             |     |

| Table 19 | THD and $\Delta THD$ of the flyback converter with ARC for all the studied cases                               | 149 |

| Table 20 | Summary of the optimization results of the Flyback converter with ARC                                          |     |

| Table 21 | Values used in the simulation of the IBuFly converter                                                          | 158 |

| Table 22 | Simulation results of the IBuFly converter                                                                                                      |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 23 | Cases studied in the IBuFly                                                                                                                     |

| Table 24 | Bus capacitance and $\Delta C_{\%}$ of the IBuFly converter with ARC for all the studied cases                                                  |

| Table 25 | THD and $\Delta THD$ of the IBuFly converter with ARC for all the studied cases                                                                 |

| Table 26 | Results of the optimization procedure regarding the amplitudes of some harmonic components of the duty cycle function for the IBuFly converter  |

| Table 27 | Results of the optimization procedure regarding the amplitudes of some harmonic components of the duty cycle function for the flyback converter |

| Table 28 | Values used in the simulation of the IBoBu converter for evaluating the optimization results of the case no. 15                                 |

| Table 29 | Summary of the optimization results of the IBuFly converter with ARC 170                                                                        |

| Table 30 | Values used in the simulation of the IBoBu converter                                                                                            |

| Table 31 | Simulation results of the IBoBu converter                                                                                                       |

| Table 32 | Cases studied in the IBoBu                                                                                                                      |

| Table 33 | Bus capacitance and $\Delta C_{\%}$ of the IBoBu converter with ARC for all the studied cases                                                   |

| Table 34 | THD and $\Delta THD$ of the IBoBu converter with ARC for all the studied cases                                                                  |

| Table 35 | Summary of the optimization results of the IBoBu converter with ARC 180                                                                         |

| Table 36 | Values used in the simulation of the IBoBu converter for evaluating the optimization results of the case no. 3                                  |

| Table 37 | Values used in the simulation of the IBuFly converter                                                                                           |

| Table 38 | Simulation results of the IDBB converter                                                                                                        |

| Table 39 | Cases studied in the IDBB converter                                                                                                             |

| Table 40 | Bus capacitance and $\Delta C_{\%}$ of the IDBB converter with ARC for all the studied cases                                                    |

| Table 41 | THD and $\Delta THD$ of the IDBB converter with ARC for all the studied                                                                         |

|          | cases                                                                  | 189   |

|----------|------------------------------------------------------------------------|-------|

| Table 42 | Summary of the optimization results for the IDBB converter with ARC $$ | 190   |

| Table 43 | Parameters for the design of the IDBB converter                        | 207   |

| Table 44 | Components of the current sensor                                       | . 208 |

| Table 45 | Range of the optimization variables.                                   | 208   |

| Table 46 | Values used in the simulation of the IDBB converter.                   | 216   |

| Table 47 | Simulation results of the IDBB converter for $w_{opt} = 1$             | 217   |

| Table 48 | Simulation results of the IDBB converter for $w_{opt} = 0$             | 219   |

| Table 49 | Prototype parameters                                                   | . 221 |

## LIST OF ABBREVIATIONS

**ABNT** Association of Technical Standards (Associação Brasileira de Normas Técnicas)

ac alternating current

Al-Caps Aluminum Electrolytic Capacitors

AP-Caps Aluminum Polymer Capacitors

**ARC** Active Ripple Compensation

**ARCT** Active Ripple-Compensation Technique

**BCM** Boundary Conduction Modes

**CCM** Continuous Conduction Mode

**CCT** correlated color temperature

CMC current-mode control

CRI color rendering index

dc direct current

**DCM** Discontinuous Conduction Mode

EMI electromagnetic interference

**ES** Exhaustive Search

ESR Equivalent Series Resistence

**FIT** Failures in Time

**FoM** figure of merit

$\mathbf{HPF}$  High Power Factor

**HPS** High-pressure Sodium

IBuFly Integrated Buck Flyback Converter

IDBB Integrated Double Buck-Boost

**IHS** Information Handling Services

INMETRO Instituto Nacional de Metrologia, Qualidade e Tecnologia

**ISBB** Integrated SEPIC buck-boost

**LED** Light-emitting Diode

LFR Low-frequency Ripple

MLC-Caps Multilayer Ceramic Capacitors

MPPF-Caps Metallized Polypropylene Film Capacitors

MTBF Mean-Time Between Failures

PC Power Control

PC-LED Phosphor-converted LED

POHC Partial Odd Harmonic Current

PF power factor

**PFC** Power Factor Correction

**RGB** Red-Green-Blue

SMPS switched-mode power supplies

SRC Series Resonant Converter

SSL Solid-State Lighting

**THD** Total Harmonic Distortion

VMC voltage-mode control

**ZCS** zero current switching

**ZCD** zero cross detector

## CONTENTS

|                                                                                                                                                                 | 35                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 1.1 EVOLUTION OF LIGHTING TECHNOLOGIES                                                                                                                          | 35                                                               |

| 1.2 LIGHT-EMITTING DIODES AS A LIGHT SOURCE                                                                                                                     | 37                                                               |

| 1.2.1 Working principle and characteristics                                                                                                                     | 37                                                               |

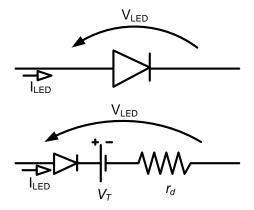

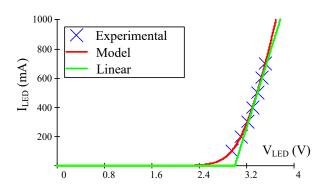

| 1.2.2 Electrical Model                                                                                                                                          | 39                                                               |

| 1.2.3 Influence of the temperature and the electrical power on the optical performance of the LEDs                                                              | 41                                                               |

| 1.2.4 Influence of the current waveform on the performance of the LEDs                                                                                          | 42                                                               |

| 1.2.5 Human biological effects of the light flicker                                                                                                             | 44                                                               |

| 1.3 LED DRIVERS                                                                                                                                                 | 45                                                               |

| 1.4 CONTENT OF THE WORK                                                                                                                                         | 47                                                               |

| 2 SINGLE PHASE POWER FACTOR CORRECTION TECHNIQUES                                                                                                               | 49                                                               |

|                                                                                                                                                                 |                                                                  |

| 2.1 POWER FACTOR CORRECTION STANDARDS                                                                                                                           | 49                                                               |

| 2.1 POWER FACTOR CORRECTION STANDARDS                                                                                                                           |                                                                  |

| <ul> <li>2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES</li> <li>2.2.1 Applications of passive pre-regulators in High Power Factor (HPF)</li> </ul>             | 51                                                               |

| 2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES                                                                                                                  | 51                                                               |

| <ul> <li>2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES</li> <li>2.2.1 Applications of passive pre-regulators in High Power Factor (HPF)</li> </ul>             | 51<br>51                                                         |

| 2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES                                                                                                                  | 51<br>51                                                         |

| <ul> <li>2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES</li> <li>2.2.1 Applications of passive pre-regulators in High Power Factor (HPF)  LED drivers</li></ul> | 51<br>51<br>52                                                   |

| <ul> <li>2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES</li> <li>2.2.1 Applications of passive pre-regulators in High Power Factor (HPF) LED drivers</li></ul>  | 51<br>51<br>52<br>53                                             |

| <ul> <li>2.2 PASSIVE POWER FACTOR CORRECTION TECHNIQUES</li></ul>                                                                                               | <ul><li>51</li><li>51</li><li>52</li><li>53</li><li>53</li></ul> |

| 2.3.2.1 VMC boost PFC pre-regulator                                         | 60      |

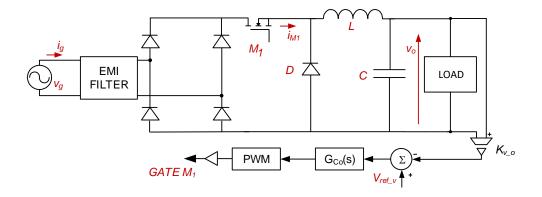

|-----------------------------------------------------------------------------|---------|

| 2.3.2.2 VMC buck-type PFC pre-regulators                                    | 62      |

| 2.3.2.3 VMC buck-boost-type PFC pre-regulators                              | 64      |

| 2.3.2.4 Applications of VMC pre-regulators in LED drivers                   | 65      |

| 2.4 SUMMARY OF THE CHAPTER                                                  | 65      |

| 3 OFF-LINE LED DRIVERS WITH REDUCED STORAGE CAPAC-                          | -       |

| ITANCE                                                                      | 67      |

| 3.1 TECHNOLOGIES OF CAPACITORS                                              | 68      |

| 3.1.1 <b>Reliability</b>                                                    | 68      |

| 3.1.2 <b>Power density</b>                                                  | 71      |

| 3.2 HIGH-VOLTAGE RIPPLE FILTERING (HVRF)                                    | 73      |

| 3.3 MULTI-STAGE CONVERTERS                                                  | 76      |

| 3.3.1 Converters based on the cascade connection of basic dc-dc topolo-     |         |

| gies                                                                        | 76      |

| 3.3.2 Converters with a resonant stage                                      | 78      |

| 3.3.3 Converters with reduced energy processing                             | 79      |

| 3.4 HARMONIC CURRENT INJECTION                                              | 82      |

| 3.5 SUMMARY OF THE CHAPTER                                                  | 83      |

| 4 REDUCING THE LOW FREQUENCY RIPPLE IN OFF-LINE LED                         | )       |

| DRIVERS BY USING LARGE SIGNAL DUTY CYCLE MODULA-<br>TION                    | -<br>85 |

| 4.1 INVESTIGATION OF THE ARC TECHNIQUE IN A FLYBACK CON-                    |         |

| VERTER                                                                      | 87      |

| 4.1.1 Design Example                                                        | 91      |

| 4.1.1.1 Design of the passive elements and the parameters of the duty cycle |         |

| function                                                                    | 92      |

| 4.1.1.2 Design of the control loop                                          | 97      |

|                                                                                                                                                                                                                                                                                                                                                    | 100                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 4.1.2 Experimental results                                                                                                                                                                                                                                                                                                                         | 102                                                  |

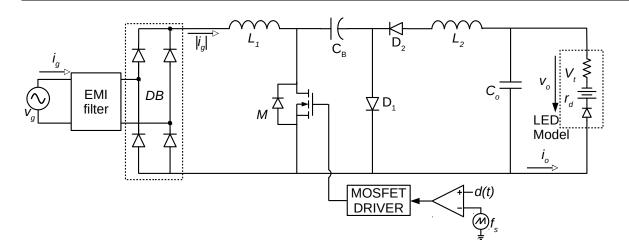

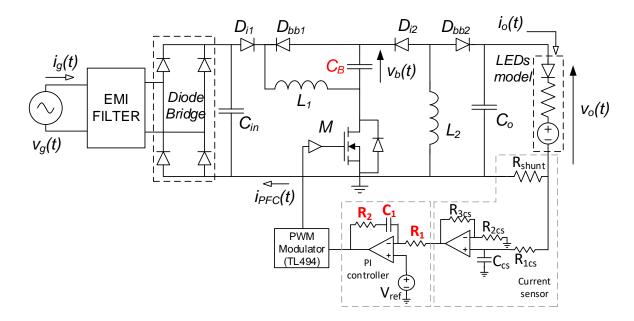

| 4.2 INVESTIGATION OF THE DUTY CYCLE MODULATION IN AN INTEGRATED TOPOLOGY                                                                                                                                                                                                                                                                           | 108                                                  |

| 4.2.1 Analysis of the IDBB converter with duty cycle modulation                                                                                                                                                                                                                                                                                    | 110                                                  |

| 4.2.2 Design procedure                                                                                                                                                                                                                                                                                                                             | 113                                                  |

| 4.2.2.1 Definition of the duty cycle function and calculation of the passive elements                                                                                                                                                                                                                                                              | 114                                                  |

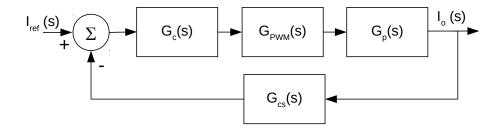

| 4.2.2.2 Design of the control loop                                                                                                                                                                                                                                                                                                                 |                                                      |

| 4.2.3 Simulation results                                                                                                                                                                                                                                                                                                                           |                                                      |

| 4.2.4 Experimental results                                                                                                                                                                                                                                                                                                                         |                                                      |

| 4.3 SUMMARY OF THE CHAPTER                                                                                                                                                                                                                                                                                                                         |                                                      |

|                                                                                                                                                                                                                                                                                                                                                    | 101                                                  |

| 5 OPTIMIZED DESIGN OF LED DRIVERS WITH ACTIVE RIPPLE                                                                                                                                                                                                                                                                                               | 3                                                    |

|                                                                                                                                                                                                                                                                                                                                                    | 133                                                  |

|                                                                                                                                                                                                                                                                                                                                                    | 133                                                  |

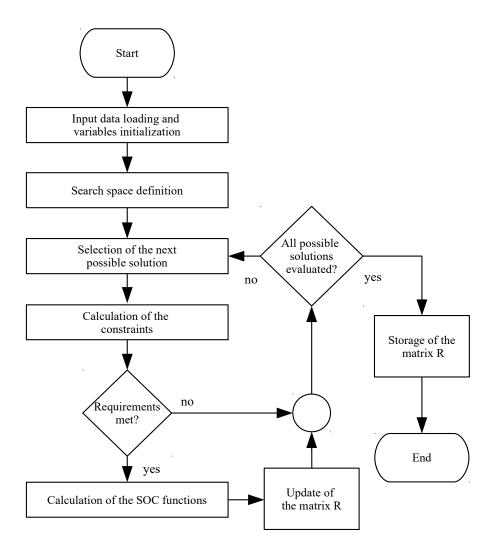

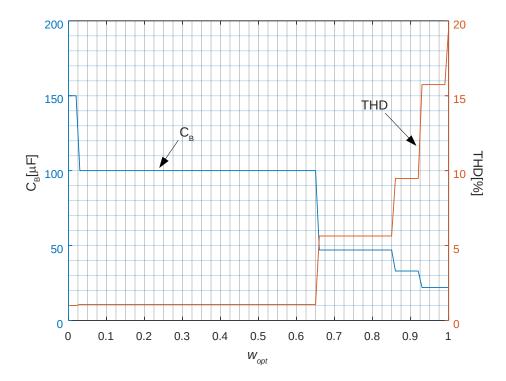

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZA-                                                                                                                                                                                                                                                                   | <b>133</b> 134                                       |

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZATION PROBLEM                                                                                                                                                                                                                                                        | 134<br>137                                           |

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZATION PROBLEM  5.2 DESIGN PROCEDURE                                                                                                                                                                                                                                  | 134<br>137<br>139                                    |

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZATION PROBLEM  5.2 DESIGN PROCEDURE  5.3 FLYBACK CONVERTER                                                                                                                                                                                                           | 133<br>134<br>137<br>139<br>140                      |

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZATION PROBLEM  5.2 DESIGN PROCEDURE  5.3 FLYBACK CONVERTER  5.3.1 Main equations                                                                                                                                                                                     | 133<br>134<br>137<br>139<br>140<br>141               |

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZATION PROBLEM  5.2 DESIGN PROCEDURE  5.3 FLYBACK CONVERTER  5.3.1 Main equations  5.3.2 Simulation results                                                                                                                                                           | 133<br>134<br>137<br>139<br>140<br>141<br>143        |

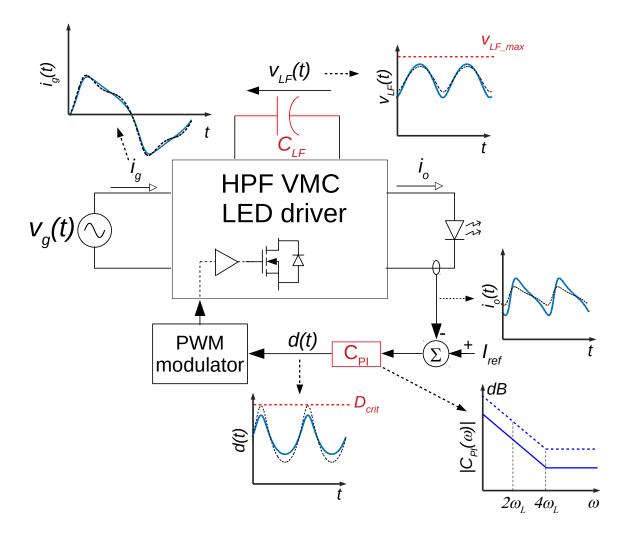

| COMPENSATION CONTROL  5.1 DESIGN OF LED DRIVERS BASED ON A CONSTRAINED OPTIMIZATION PROBLEM  5.2 DESIGN PROCEDURE  5.3 FLYBACK CONVERTER  5.3.1 Main equations  5.3.2 Simulation results  5.3.3 Description of the design conditions and the search space                                                                                          | 133<br>134<br>137<br>139<br>140<br>141<br>143<br>146 |