# UNIVERSIDADE FEDERAL DE JUIZ DE FORA FACULDADE DE ENGENHARIA PROGRAMA DE PÓS GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Lucca Oliveira Facio Viccini

Simulation and Testing of the Upgraded Digital Signal Processing Firmware Using High-Level Synthesis on the Real-Time Trigger Path of the ATLAS Liquid Argon Calorimeters

# Lucca Oliveira Facio Viccini

Simulation and Testing of the Upgraded Digital Signal Processing Firmware

Using High-Level Synthesis on the Real-Time Trigger Path of the ATLAS

Liquid Argon Calorimeters

Dissertação apresentada ao Programa de Pós Graduação em Engenharia Elétrica da Universidade Federal de Juiz de Fora como requisito parcial à obtenção do título de Mestre em Engenharia Elétrica. Área de concentração: Sistemas Eletrônicos

Orientador: Prof. Dr Luciano Manhães de Andrade Filho

Coorientador: Dr. Marcos Vinícius Silva Oliveira

Ficha catalográfica elaborada através do Modelo Latex do CDC da UFJF com os dados fornecidos pelo(a) autor(a)

Oliveira Facio Viccini, Lucca.

Simulation and Testing of the Upgraded Digital Signal Processing Firmware Using High-Level Synthesis on the Real-Time Trigger Path of the ATLAS Liquid Argon Calorimeters / Lucca Oliveira Facio Viccini. – 2025.

111 f. : il.

Orientador: Luciano Manhães de Andrade Filho Coorientador: Marcos Vinícius Silva Oliveira

Dissertação (Mestrado) — Universidade Federal de Juiz de Fora, Faculdade de Engenharia. Programa de Pós Graduação em Engenharia Elétrica, 2025.

1. High Energy Physics. 2. FPGA. 3. High-Level Synthesis. 4. Functional Simulation, 5. Low latency. I. Manhães de Andrade Filho, Luciano, orient. II. Silva Oliveira, Marcos Vinícius. coorient. III. Título.

# FEDERAL UNIVERSITY OF JUIZ DE FORA RESEARCH AND GRADUATE PROGRAMS OFFICE

#### Lucca Oliveira Facio Viccini

Simulation and Testing of the Upgraded Digital Signal Processing Firmware Using High-Level Synthesis on the Real-Time Trigger Path of the ATLAS Liquid Argon Calorimeters

Thesis submitted to the Graduate Program in Electrical Engineering of the Federal University of Juiz de Fora as a partial requirement for obtaining a Master's degree in Electrical Engineering.

Concentration area: Electronic Systems

Approved on 18 of September of 2025.

#### **EXAMINING BOARD**

**Prof. Dr. Luciano Manhães de Andrade Filho** – Academic Advisor Federal University of Juiz de Fora

**Prof. Dr. Marcos Vinícius Silva Oliveira –** Academic Co-Advisor Brookhaven National Laboratory

> **Prof. Dr. Leandro Rodrigues Manso Silva** Federal University of Juiz de Fora

**Prof. Dr. Victor Araujo Ferraz**Federal University of Rio Grande do Norte

Juiz de Fora, 09/18/2025.

Documento assinado eletronicamente por **Leandro Rodrigues Manso Silva**, **Professor(a)**, em 22/09/2025, às 10:47, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por **Marcos Vinicius Silva Oliveira**, **Usuário Externo**, em 25/09/2025, às 13:07, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do <u>Decreto nº 10.543, de 13 de novembro de 2020</u>.

Documento assinado eletronicamente por **Luciano Manhaes de Andrade Filho**, **Professor(a)**, em 02/10/2025, às 19:10, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por **Victor Araujo Ferraz**, **Usuário Externo**, em 07/10/2025, às 12:50, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do <u>Decreto nº 10.543, de 13 de novembro de 2020</u>.

A autenticidade deste documento pode ser conferida no Portal do SEI-Ufjf (www2.ufjf.br/SEI) através do ícone Conferência de Documentos, informando o código verificador **2624904** e o código CRC **4FEFDD8C**.

#### **AGRADECIMENTOS**

Agradeço, em primeiro lugar, à minha família pelo apoio incondicional e incentivo em todas as etapas da minha vida acadêmica. Sem o suporte deles, esta conquista jamais seria possível.

À minha noiva, Nathalia, por ser meu porto seguro, meu ponto de luz, por me motivar e por estar sempre ao meu lado em todos os momentos.

Aos colegas da equipe LATOME HLS, sempre solícitos e dispostos a ajudar, independentemente do momento.

Ao meu orientador, Luciano, por todos os aprendizados e confiança depositada em mim.

Ao meu coorientador, Marcos, pela oportunidade oferecida e com quem tanto aprendi nesta jornada.

A todos os professores, pelos ensinamentos e pelo apoio neste período de estudos.

Ao professor André Marcato, por seus ensinamentos, apoio, amizade e paciência ao longo deste período.

Ao professor Ivo, por toda a paciência e apoio durante esta jornada.

À Universidade Federal de Juiz de Fora, à Faculdade de Engenharia Elétrica, ao grupo do Calorímetro de Argônio Líquido, ao ATLAS e ao Centro Europeu de Pesquisa Nuclear (CERN), que me proporcionaram toda a infraestrutura para o desenvolvimento deste trabalho.

#### **RESUMO**

Esta dissertação apresenta a validação e simulação do pipeline digital de processamento de sinais no sistema de gatilho do Calorímetro de Argônio Líquido (LAr) do experimento ATLAS, com foco específico no firmware LATOME. A implementação utiliza High-Level Synthesis (HLS) para gerar os blocos Input Switch Matrix (ISM) e Output Summing (OSUM), responsáveis pela reorganização, processamento e agregação dos dados de Super Células em tempo real, atravessando múltiplos domínios de relógio. As versões de firmware 6.0 a 6.3 foram analisadas em profundidade, com as versões iniciais centradas no caminho de monitoramento e na validação do bloco REMAP, enquanto versões posteriores introduziram suporte aos caminhos de processamento eFEX e jFEX. Adotou-se uma estratégia de simulação em múltiplas camadas, combinando modelos Firmware-Agnostic e Firmware-Aware para possibilitar testes abrangentes desde componentes HLS isolados até o firmware integrado completo. Os principais esforços de validação incluíram a calibração do atraso do sinal SOP, a identificação da janela de metastabilidade e a verificação funcional dos mecanismos de sincronização entre domínios de relógio. A integração do módulo de diagnóstico Mini-FEX permitiu a observação em tempo real de erros de SOP e CRC, tanto em simulações quanto durante a operação do sistema ATLAS. A metodologia desenvolvida ao longo deste trabalho oferece uma estrutura reutilizável e escalável para validar futuras versões do firmware—como o caminho gFEX (v6.4) e o bloco User Code (v7.x)—e serve como referência para a adoção de HLS em outros sistemas FPGA de alta taxa de dados e baixa latência em experimentos de física de altas energias.

Palavras-chave: high-level synthesis; firmware latome; calorímetro de argônio líquido do ATLAS; sistema de gatilho em tempo real; validação e simulação em fpga.

#### **ABSTRACT**

This thesis presents the validation and simulation of the upgraded digital signal processing pipeline deployed in the ATLAS Liquid Argon Calorimeter trigger system, with a particular focus on the LATOME firmware. The implementation relies on High-Level Synthesis (HLS) to generate the Input Switch Matrix (ISM) and Output Summing (OSUM) blocks, which are responsible for reorganizing, processing, and aggregating real-time Super Cell data across multiple clock domains. Firmware versions 6.0 through 6.3 were analyzed in depth, with early versions centered on the monitoring path and REMAP validation, and later iterations introducing support for eFEX and jFEX trigger paths. A multilayered simulation strategy was adopted, combining Firmware-Agnostic and Firmware-Aware models to enable comprehensive testing from standalone HLS components to fully integrated firmware deployments. Key validation efforts included SOP delay calibration, metastability window identification, and functional verification of clock synchronization logic. The integration of the Mini-FEX diagnostic module provided real-time observability of SOP and CRC errors, both in simulation and during ATLAS system operation. The methodology developed throughout this work offers a reusable and scalable framework for validating future firmware upgrades—such as the gFEX path (v6.4) and the User Code block (v7.x)—and serves as a reference for adopting HLS in other high-throughput, low-latency FPGA-based systems in high-energy physics experiments.

**Keywords:** high-level synthesis; latome firmware; atlas liquid argon calorimeter; real-time trigger system; fpga validation and simulation.

# List of Figures

| Figure 1 – Overview of the LHC accelerator ring and its four main experimental sit      | ies                    |

|-----------------------------------------------------------------------------------------|------------------------|

| ATLAS, CMS, ALICE, and LHCb [5]                                                         | 15                     |

| Figure 2 $-$ Schematic view of the ATLAS detector, illustrating its primary subsystems: | the                    |

| Inner Detector, Calorimeters, Magnet System, and Muon Spectrometer [11].                | 20                     |

| Figure 3 – Transversal slice of the ATLAS detector, illustrating its primary subsyste   | ms                     |

| and the typical paths of different particle types as they interact with the Int         | ner                    |

| Detector, Calorimeters, and Muon Spectrometer                                           | 21                     |

| Figure 4 - Cut-away view of the ATLAS calorimeter system, comprising the Liquid Arg     | gon                    |

| electromagnetic calorimeters and the Tile hadronic calorimeter                          | 22                     |

| Figure 5 – Overview of the ATLAS Trigger and Data Acquisition (TDAQ) system, show       | ing                    |

| the data flow from detector readout through the Level-1 hardware trigger a              | $\operatorname{ind}$   |

| the High-Level software trigger to offline storage [16]                                 | 23                     |

| Figure 6 – Timeline of the LHC operational schedule, including Runs, Long Shutdow       | $^{\prime}\mathrm{ns}$ |

| and the transition to the High-Luminosity LHC (HL-LHC) [21]                             | 25                     |

| Figure 7 – Diagram of the ATLAS Liquid Argon Calorimeter, showing its four ma           | ain                    |

| regions: EMB, EMEC, HEC, and FCAL                                                       | 27                     |

| Figure 8 – The ATLAS LAr calorimeter trigger readout system. Signals are digitized      | by                     |

| the LTDBs, processed by the LATOMEs in the back-end, and transmitted                    | te                     |

| both the L1Calo Feature Extractors (eFEX, jFEX, gFEX) for triggering a                  | $\operatorname{nd}$    |

| the FELIX system for data acquisition and monitoring                                    | 29                     |

| Figure 9 – Comparison between the legacy Trigger Tower segmentation and the Pha         | ıse                    |

| I Super Cell segmentation. Super Cells provide finer granularity, presen                | rve                    |

| longitudinal layer information, and improve trigger performance                         | 30                     |

| Figure 10 – LAr Carrier (LArC) ATCA board hosting four LATOME boards                    | 31                     |

| Figure 11 – A close-up view of a LATOME board, showing the heat sink, the four MTP-     | -12                    |

| optical input connectors (green), and the MTP-48 output connector (black).              | 32                     |

| Figure 12 – LATOME firmware block diagram. The pale brown frame corresponds             | tc                     |

| the hardware interface, while the blue boxes represent higher-level function            | nal                    |

| blocks [6]                                                                              | 38                     |

| Figure 13 – LATOME firmware clock domains block diagram [6]                             | 39                     |

| Figure $14$ – Three-step remapping implementation in the LATOME v5 firmware             | 40                     |

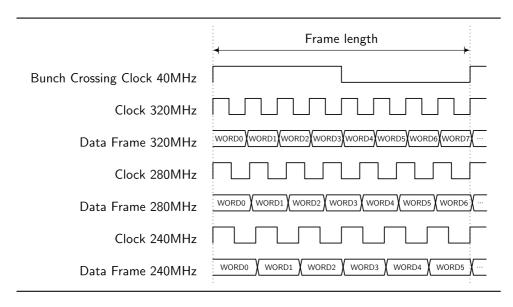

| Figure 15 – Timing diagram illustrating the clock frequencies and word configurations   | in                     |

| the v5 LATOME firmware [23]                                                             | 41                     |

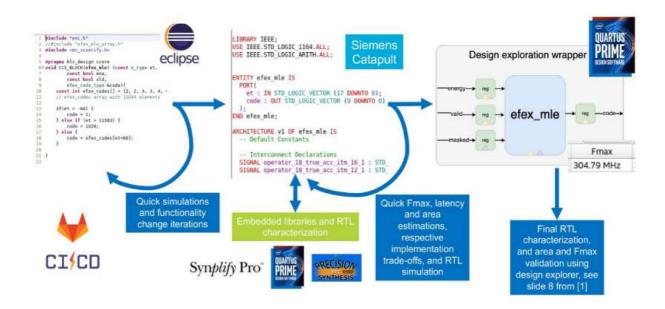

| Figure 16 – Design flow from C++ to VHDL using Siemens Catapult                         | 45                     |

| Figure 17 – VHDL Wrapper Generator GUI. The user pastes the Catapult-generated VH       |                        |

| entity (top), selects flattened ports (middle), and receives a new wrapper ent          | ity                    |

| and package (bottom) for easier signal handling                                         | 46                     |

|                                                                                         |                        |

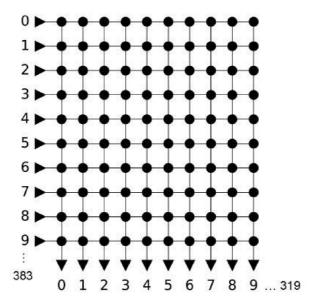

| Figure 18 – I   | Diagram of the switch matrix architecture in the REMAP block. Black dots       |

|-----------------|--------------------------------------------------------------------------------|

| i               | ndicate programmable interconnections between input and output streams. 48     |

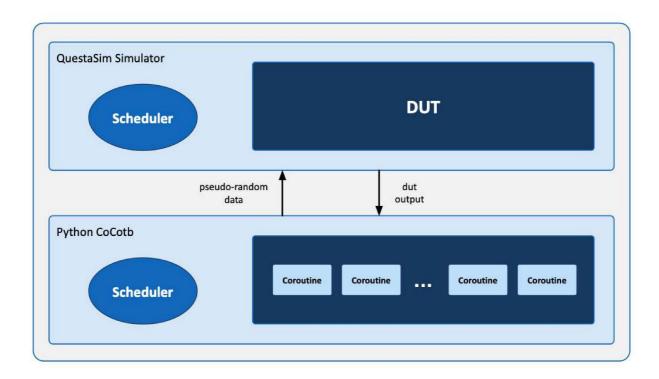

| Figure 19 – I   | nteraction between Cocotb and QuestaSim, showcasing coroutine-based simu-      |

| 1               | ation and probing of multiple circuit points                                   |

| Figure 20 – N   | Monitoring path dataflow in the legacy LATOME firmware (v5) 53                 |

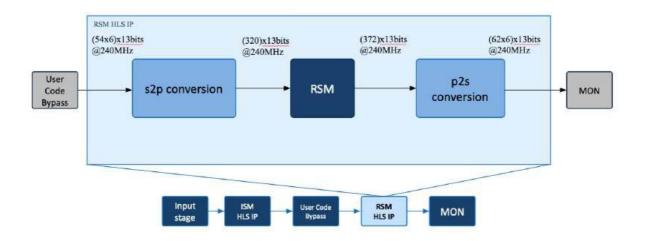

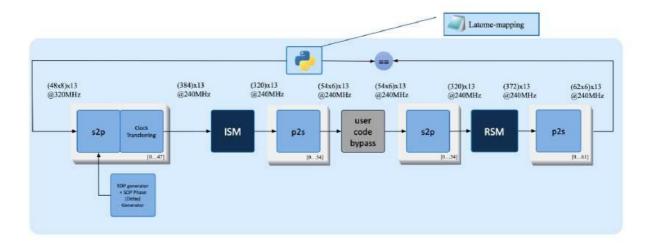

| Figure 21 – I   | Demonstration firmware architecture (v6.0.0), with the legacy remapping        |

| r               | replaced by an HLS-based Input Switch Matrix (ISM) 53                          |

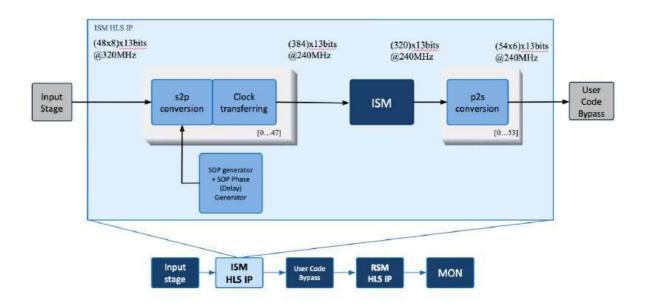

| Figure 22 – I   | Block diagram of the ISM HLS IP. Each input passes through an S2P converter    |

| V               | with clock transfer, followed by the parallel switch matrix (ISM) and the P2S  |

| (               | converter                                                                      |

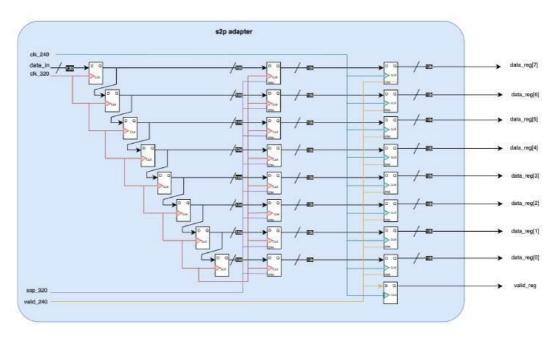

| Figure 23 – I   | nternal structure of a Serial-to-Parallel (S2P) converter with clock transfer, |

| ŀ               | oridging 320 MHz serialized data to the 240 MHz domain                         |

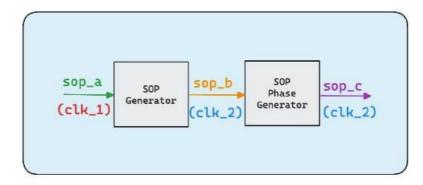

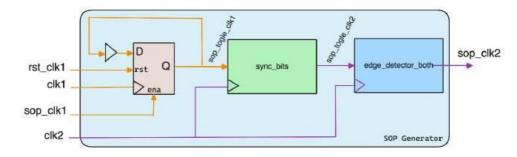

| Figure 24 – 0   | Connection between the SOP generator and the SOP phase generator, provid-      |

| i               | ng synchronization and phase selection for the S2P modules                     |

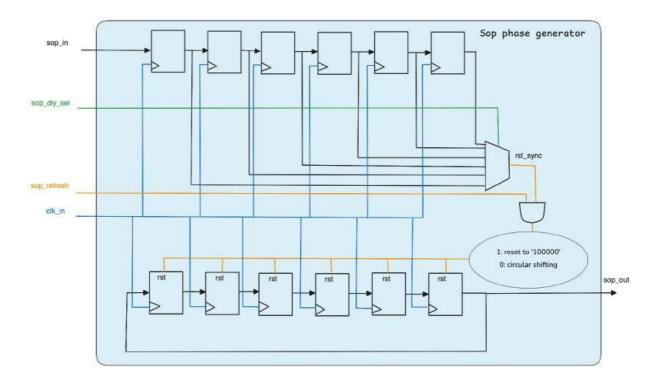

| Figure $25 - 5$ | SOP generator: produces a reference pulse that marks the start of each bunch   |

| (               | crossing and distributes it to the S2P converters                              |

| Figure 26 – S   | SOP phase generator: introduces a programmable delay to the reference pulse,   |

| $\epsilon$      | ensuring that data capture in the 240 MHz domain occurs at a stable and        |

| (               | controlled instant                                                             |

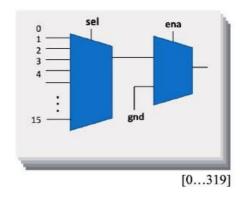

| Figure 27 – S   | Structure of the ISM highlighting the two cascaded multiplexers 57             |

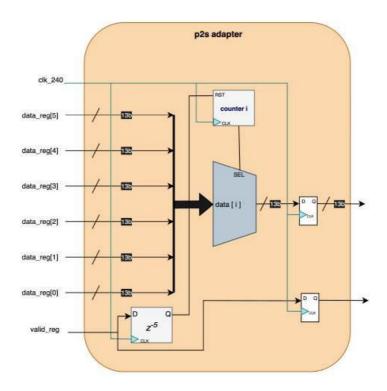

| Figure 28 – A   | Architecture of the P2S adapter used to serialize six 13-bit words from the    |

| J               | Jser Code output                                                               |

| Figure 29 – A   | Architecture of the RSM HLS IP. The S2P and P2S modules match those in         |

| t               | he ISM, but operate within a single clock domain                               |

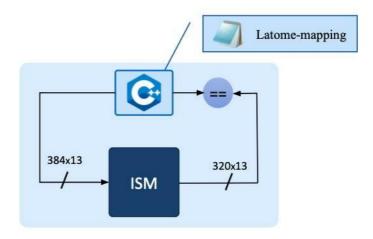

| Figure $30 - I$ | Layer 0: Functional verification of the ISM logic using a C++ implementation   |

| 8               | and mapping files                                                              |

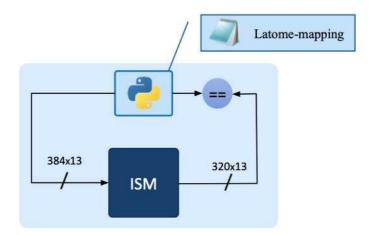

| Figure $31 - F$ | Python-based RTL validation of the ISM block using Cocotb. Tests include       |

| s               | signal-level monitoring of the VHDL output 61                                  |

| Figure 32 – I   | Example waveform from Cocotb/QuestaSim showing synchronization using           |

| t               | he bcid signal to validate output after the fixed latency of the ISM block. 63 |

| Figure 33 – 0   | Cocotb testbench for the full monitoring chain of firmware version 6.0.0.      |

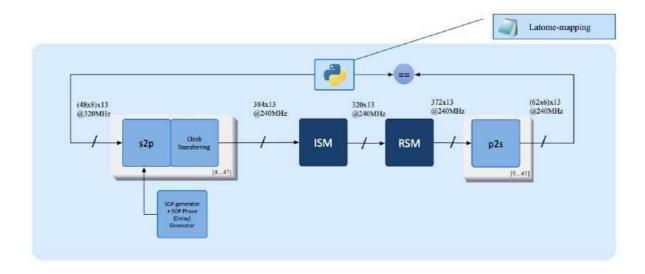

| I               | ncludes S2P with clock transferring, ISM, RSM, and P2S blocks 64               |

| Figure 34 – I   | Extended testbench including User Code bypass to directly validate ISM-RSM     |

| (               | compatibility                                                                  |

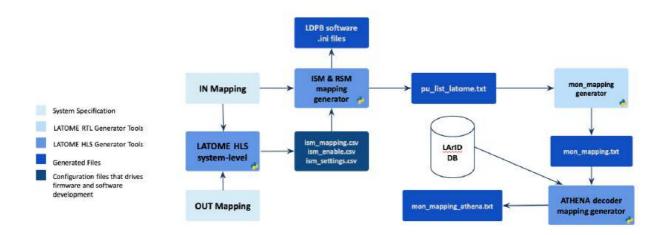

| Figure 35 – I   | LATOME HLS software infrastructure                                             |

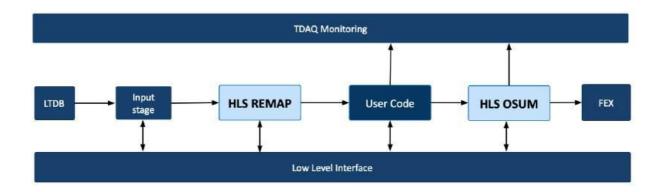

| Figure 36 – S   | Simplified trigger path architecture from firmware version 6.2 onward high-    |

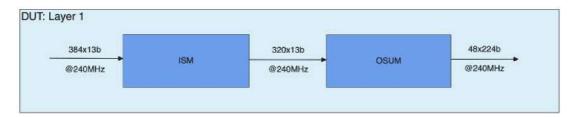

| 1               | ighting both HLS designed blocks 70                                            |

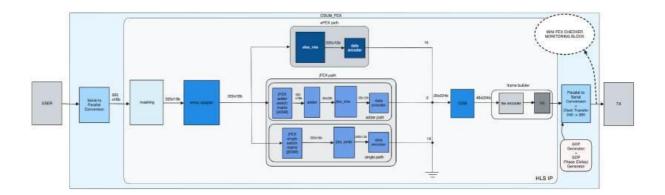

| Figure 37 – Block diagram of the OSUM HLS IP showing the eFEX output path. The            |  |

|-------------------------------------------------------------------------------------------|--|

| figure highlights the sequential pipeline stages from the User Code to the final          |  |

| transmission to the FEX system, including key clock domain boundaries and                 |  |

| data formatting blocks                                                                    |  |

| Figure 38 – Bit layout of the eFEX data frame constructed by efex_data. The CRC field     |  |

| is not yet valid at this stage                                                            |  |

| Figure 39 – Structure of the eFEX align frame                                             |  |

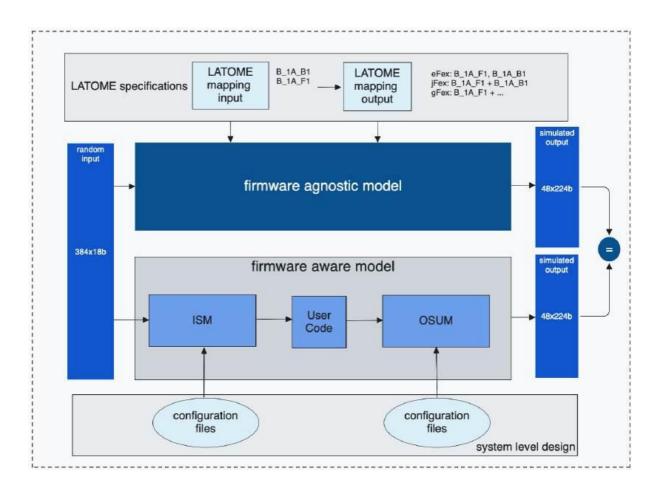

| Figure 40 – Firmware Aware and Agnostic Models                                            |  |

| Figure 41 – Simulation strategy for Layer 1: isolated HLS block verification in a single  |  |

| clock domain                                                                              |  |

| Figure 42 – Simulation strategy for Layer 2: verification of blocks across clock domain   |  |

| boundaries using SerDes                                                                   |  |

| Figure 43 – Simulation strategy for Layer 3: full-firmware validation including User Code |  |

| and output logic                                                                          |  |

| Figure 44 – Mini-FEX diagnostic output during laboratory testing. All counters incre-     |  |

| mented as expected and no SOP-related or CRC errors were observed $85$                    |  |

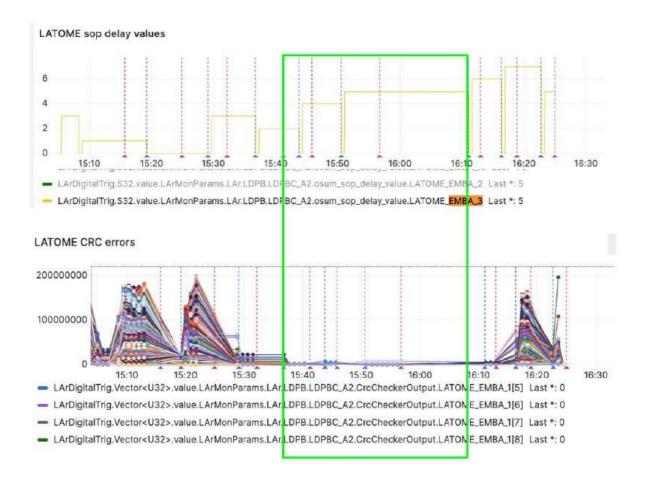

| Figure 45 – Grafana dashboard from a P1 run showing OSUM SOP-delay values (top) and       |  |

| corresponding CRC error counters (bottom). The highlighted period shows                   |  |

| stable operation after configuration                                                      |  |

| Figure 46 – OSUM block diagram showing the integrated jFEX path 88                        |  |

| Figure 47 – Bit layout of the jFEX data frame constructed by jfex_data. The K28.5         |  |

| symbol replaces SATUR[7:0] when no saturation is detected 91                              |  |

| Figure 48 – Structure of the jFEX align frame. Includes FEX ID, fiber ID, full BCID,      |  |

| LATOME identifiers, and frame boundary markers                                            |  |

| Figure 49 – Comparison between golden model and firmware outputs for the REMAP            |  |

| block. All values match                                                                   |  |

| Figure 50 – Example of mismatch detection in OSUM output: BC, frame, word, expected       |  |

| value (model), and actual value (DUT) are shown                                           |  |

| Figure 51 – Cocotb simulation summary showing successful validation of the complete       |  |

| LATOME HLS DUT (REMAP and OSUM blocks included) 96                                        |  |

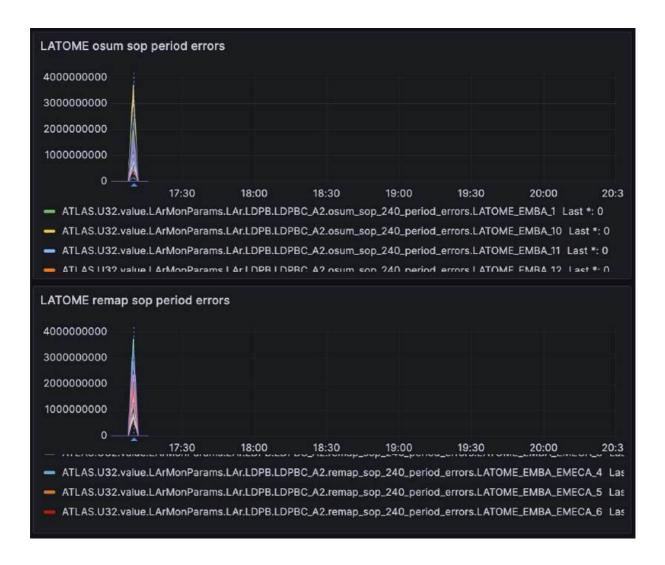

| Figure 52 – SOP period error counters for the REMAP and OSUM blocks during ATLAS          |  |

| online testing. Errors are observed at startup but converge to zero after                 |  |

| sop_refresh is disabled                                                                   |  |

| Figure 53 – Evolution of CRC errors and sop_refresh values over time. The drop in         |  |

| errors aligns with the moment the $sop_refresh$ signal is set to zero 102                 |  |

|                                                                                           |  |

# List of Tables

| Table 1 -  | Active Super Cell inputs per region according to the official LATOME input                |

|------------|-------------------------------------------------------------------------------------------|

|            | mapping files                                                                             |

| Table 2 -  | Percentage of success on complete tests for firmware version $v6.0.0$ using the           |

|            | EMBA_1 mapping (50 completed tests)                                                       |

| Table 3 -  | Percentage of success on complete tests for firmware version $v6.0.0$ across              |

|            | LATOME mappings                                                                           |

| Table 4 -  | Percentage of success on complete tests for firmware version v6.1.0 using the             |

|            | EMBA_1 mapping (50 completed tests)                                                       |

| Table 5 -  | Percentage of success on complete tests for firmware version $v6.1.0$ across              |

|            | LATOME mappings                                                                           |

| Table 6 -  | Percentage of success on complete tests for firmware version $v6.2.0$ using the           |

|            | EMBA_1 mapping (50 completed tests)                                                       |

| Table 7 -  | Percentage of success on complete tests for firmware version v6.2.0 across                |

|            | LATOME mappings                                                                           |

| Table 8 -  | SOP-delay scan in the Point 1 system with ${\tt remap}$ fixed at 2 and ${\tt osum}$ swept |

|            | from 0 to 7                                                                               |

| Table 9 -  | Percentage of success on complete tests for firmware version v6.3.0 using the             |

|            | EMBA_1 mapping (50 completed tests)                                                       |

| Table 10 - | Percentage of success on complete tests for firmware version v6.3.0 across                |

|            | LATOME mappings                                                                           |

| Table 11 - | Stress test results for the OSUM block on the EMBA_1 mapping, with 50 runs                |

|            | per $sop_delay_select$ configuration. All values represent the percentage of              |

|            | tests (out of $50$ ) in which errors were detected or data matched successfully. $99$     |

| Table 12 - | OSUM validation results with $sop\_refresh$ deasserted after 1 second of ini-             |

|            | tialization, using the EMBA $\_1$ mapping. Each $\mathtt{sop\_delay\_select}$ was tested  |

|            | over 50 runs. The REMAP SOP was fixed at delay 2 for all tests. All values                |

|            | represent the percentage of tests in which errors were detected or successful             |

|            | outcomes achieved                                                                         |

# LISTA DE ABREVIATURAS E SIGLAS

ADC Analog-to-Digital Converter

ALICE A Large Ion Collider Experiment

AMC Advanced Mezzanine Card

ATCA Advanced Telecommunications Computing Architecture

ATLAS A Toroidal LHC ApparatuS

BC Bunch Crossing

BCID Bunch Crossing Identifier

CERN Conseil Européen pour la Recherche Nucléaire

CMS Compact Muon Solenoid

CRC Cyclic Redundancy Check

CDC Clock Domain Crossing

DAQ Data Acquisition

EMEC Electromagnetic Endcap Calorimeter eFEX Electromagnetic Feature Extractor

FEX Feature Extractor

FPGA Field-Programmable Gate Array

gFEX Global Feature Extractor

HEC Hadronic Endcap Calorimeter

HEP High-Energy Physics

HLS High-Level Synthesis

HLT High-Level Trigger

jFEX Jet Feature Extractor

LAr Liquid Argon

LArC LAr Carrier Board

LATOME LAr Trigger prOcessing MEzzanine

LDPB LAr Digital Processing Blade

LHC Large Hadron Collider LHCb LHC beauty experiment

L1 Level-1 (Trigger)

LLI Low-Level Interface

LTDB LAr Trigger Digitizer Board

OSUM Output Summing

PU Processing Unit

SC Super Cell

SM Switch Matrix

SOP Start of Packet

TDAQ Trigger and Data Acquisition

TDR Technical Design Report

TTC Timing, Trigger, and Control

UC User Code

# Contents

| T       | Introduction                                                                 |

|---------|------------------------------------------------------------------------------|

| 1.1     | Motivation                                                                   |

| 1.2     | Objectives                                                                   |

| 1.3     | Thesis Structure                                                             |

| 2       | The ATLAS Experiment                                                         |

| 2.1     | ATLAS Overview                                                               |

| 2.2     | ATLAS Subsystems                                                             |

| 2.3     | ATLAS Trigger and Data Acquisition System (TDAQ)                             |

| 2.4     | The ATLAS Detector Upgrade Program                                           |

| 3       | The Liquid Argon Calorimeter Trigger Readout Architecture 26                 |

| 3.1     | Structure of the LAr Calorimeters                                            |

| 3.2     | Overview of the LAr Trigger Readout Path                                     |

| 3.3     | Phase-I Upgrade and the Introduction of Super Cells                          |

| 3.4     | Back-End Electronics                                                         |

| 3.5     | Front-End Electronics                                                        |

| 3.6     | Timing and Synchronization                                                   |

| 3.7     | Monitoring and Data Validation                                               |

| 4       | LATOME Firmware                                                              |

| 4.1     | Firmware Functional Overview                                                 |

| 4.2     | Firmware Architecture                                                        |

| 4.3     | Legacy Design: Version $5 \ldots 40$                                         |

| 5       | Methodology and Tools                                                        |

| 5.1     | Field-Programmable Gate Arrays (FPGAs)                                       |

| 5.2     | High-Level Synthesis (HLS)                                                   |

| 5.3     | Wrapper Generator for HLS-VHDL Integration                                   |

| 5.4     | Switch Matrix Architecture                                                   |

| 5.5     | Coroutine-Based Co-Simulation with Cocotb and QuestaSim 48                   |

| 5.6     | Simulation and Validation Strategy                                           |

| 6       | Firmware Evolution and Validation: Versions $6.0$ to $6.3$ $51$              |

| 6.1     | Overview of the Firmware Evolution                                           |

| 6.2     | Demonstration Firmware Integration and HLS Validation (v6.0.0 and v6.1.0) 52 |

| 6.2.1   | S2P Converter and Clock Domain Crossing                                      |

| 6.2.2   | The Input Switch Matrix (ISM)                                                |

| 6.2.3   | Parallel-to-Serial (P2S) Adapter                                             |

| 6.2.4   | RSM HLS IP                                                                   |

| 6.2.5   | Validation Strategy and Test Campaigns                                       |

| 6.2.5.1 | Cocotb Simulation                                                            |

| 6.2.5.2   | Full Demonstration Firmware Simulation                  | 63 |

|-----------|---------------------------------------------------------|----|

| 6.2.5.3   | Transition to Firmware Version 6.1.0                    | 65 |

| 6.2.6     | Clock Domain Transfer Validation: SOP Delay Tests       | 65 |

| 6.2.6.1   | Hardware Test Environment                               | 65 |

| 6.2.6.2   | Firmware v6.0.0 Test Results                            | 66 |

| 6.2.6.3   | Firmware v6.1.0 Test Results                            | 66 |

| 6.2.7     | LATOME HLS Software Infrastructure                      | 67 |

| 6.3       | Firmware Version 6.2                                    | 69 |

| 6.3.1     | OSUM HLS Architecture                                   | 70 |

| 6.3.1.1   | Masking                                                 | 70 |

| 6.3.1.2   | EMEC Adapter                                            | 71 |

| 6.3.1.3   | eFEX MLE: Multi-Linear Encoder                          | 71 |

| 6.3.1.4   | Data Encoder: Construction of the eFEX Data Frame       | 73 |

| 6.3.1.5   | Output Switch Matrix (OSM)                              | 73 |

| 6.3.1.6   | Frame Select Block                                      | 74 |

| 6.3.1.7   | CRC-9 Calculation                                       | 75 |

| 6.3.2     | Clock Transfer and SerDes                               | 76 |

| 6.3.2.1   | Serial-to-Parallel Conversion                           | 76 |

| 6.3.2.2   | Parallel-to-Serial Conversion and Clock Domain Crossing | 77 |

| 6.3.2.3   | Mini-FEX Monitoring Logic                               | 78 |

| 6.3.3     | Simulation Strategy and Models                          | 79 |

| 6.3.3.1   | Firmware Agnostic and Firmware Aware Models             | 79 |

| 6.3.3.2   | Layered Simulation Strategy                             | 80 |

| 6.3.3.2.1 | Layer 0                                                 | 80 |

| 6.3.3.2.2 | Layer 1                                                 | 81 |

| 6.3.3.2.3 | Layer 2                                                 | 81 |

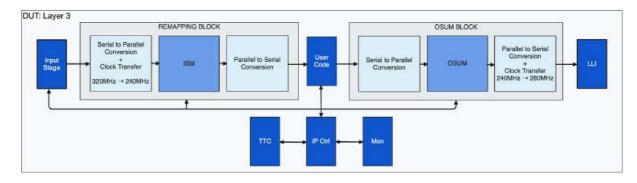

| 6.3.3.2.4 | Layer 3                                                 | 82 |

| 6.3.4     | Validation Results                                      | 82 |

| 6.3.4.1   | REMAP Validation                                        | 83 |

| 6.3.4.2   | OSUM Validation                                         | 84 |

| 6.4       | Firmware Version 6.3                                    | 87 |

| 6.4.1     | Adder Path                                              | 88 |

| 6.4.1.1   | jASM (jFEX Adder Switch Matrix)                         | 88 |

| 6.4.1.2   | Adder Blocks                                            | 89 |

| 6.4.1.3   | jFEX MLE: Multi-Linear Encoder                          | 89 |

| 6.4.1.4   | Data Encoder: Construction of the jFEX Data Frame       | 90 |

| 6.4.2     | Single Path                                             | 92 |

| 6.4.2.1   | jSSM: Single Switch Matrix                              | 92 |

| 6.4.2.2   | jFEX SMLE: Multi-Linear Encoder for Single Path         | 92 |

|           |                                                         |    |

| Integration into OSM                                |

|-----------------------------------------------------|

| Timing Closure and Clock Tree Improvements          |

| Simulation Campaign                                 |

| Hardware Validation                                 |

| REMAP Validation                                    |

| OSUM Validation                                     |

| Conclusion                                          |

| HLS Wrapper Generator Output 105                    |

| Original Entity Generated by Catapult               |

| Generated Wrapper Entity                            |

| Generated Package File                              |

| Example of LATOME Mapping Configuration: EMBA_1 108 |

| Bibliography                                        |

|                                                     |

#### 1 Introduction

High-energy physics (HEP) is the field dedicated to studying the fundamental constituents of matter and the forces governing their interactions. Its primary goal is to answer open questions about the nature of mass, the composition of dark matter, and the possible unification of fundamental forces. Over the past decades, research in this area has not only advanced our understanding of the universe but also driven technological developments in computing, medical imaging, and materials science.

Founded in 1954, the European Organization for Nuclear Research (*Conseil Européen pour la Recherche Nucléaire*, CERN) is the world's largest center for particle physics research. CERN hosts the Large Hadron Collider (LHC), the most powerful particle accelerator ever built, which enables the study of matter under extreme conditions by colliding proton beams at unprecedented energies [1, 2].

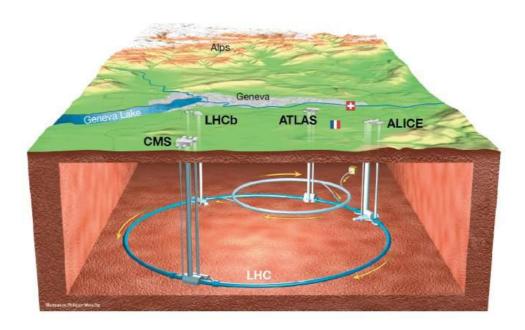

The LHC consists of a 27-kilometer underground ring located at the border between France and Switzerland, as shown in Figure 1. Proton beams are accelerated in opposite directions and are steered to collide at four designated interaction points. Each interaction point hosts a major experiment: ATLAS and CMS are general-purpose detectors designed to explore a broad range of physics phenomena, while ALICE and LHCb are dedicated to more specialized studies [3].

Figure 1 – Overview of the LHC accelerator ring and its four main experimental sites: ATLAS, CMS, ALICE, and LHCb [5].

#### 1.1 Motivation

Having established the broader context of the LHC and its experiments, this section narrows the focus to the technical challenges that motivate the development and validation of the firmware described in this thesis.

The efficacy of high-energy physics experiments, such as ATLAS, is contingent upon instrumentation capable of processing data at extreme rates with stringent precision and reliability requirements. The LHC operates in multi-year data-taking periods known as *Runs*, each separated by long shutdowns dedicated to maintenance and upgrades. With each successive Run, the LHC delivers higher luminosities, leading to increased data throughput and placing more stringent demands on real-time data processing systems.

A key performance indicator of a collider is its luminosity, which quantifies the number of potential particle collisions per unit area per second [4]. During Run 3, the LHC operates with proton-proton collisions at a center-of-mass energy of 13.6 TeV and achieves a peak luminosity of  $3 \times 10^{34} \, \mathrm{cm^{-2} s^{-1}}$  [6]. This high luminosity increases the probability of observing rare physics processes but also results in significant pile-up—an average of about 80 simultaneous interactions per bunch crossing. Such conditions place considerable demands on the ATLAS detector's data acquisition and trigger systems, which must process vast amounts of information in real time while maintaining high accuracy and low latency.

The ATLAS calorimeters play a central role in the trigger decision by providing precise energy measurements. In particular, the Liquid Argon (LAr) calorimeter, responsible for detecting electromagnetic showers from particles such as electrons and photons, delivers fine-granularity energy data that is essential for accurate event selection at the hardware trigger level [7].

Operating under the LHC's high collision rate of 40 MHz, the ATLAS detector generates an enormous volume of data every second [8]. To manage this, the Level-1 (L1) Trigger system plays a vital role by reducing the event rate from 40 MHz to a manageable 100 kHz. This rapid filtering ensures that only the most relevant events are retained for further processing, significantly reducing the burden on downstream systems. The L1 Trigger relies on precise energy measurements from the LAr calorimeter, making real-time signal processing a crucial component of ATLAS's functionality.

In preparation for Run 3, the LAr calorimeter underwent a significant upgrade to handle the increased collision rates and improve trigger decision performance [6]. This included the introduction of Super Cells (SC)—aggregations of multiple calorimeter cells—which provide finer spatial granularity for more precise energy reconstruction. To process this increased data volume, the LATOME (LAr Trigger processing MEzzanine) boards were developed as a central element of the upgraded back-end electronics. These

boards are responsible for aggregating, filtering, and preparing SC data for the Level-1 trigger system, enabling fast and accurate event selection.

To cope with the increased data throughput and architectural complexity, the LATOME firmware is undergoing a major redesign. Two critical processing blocks—REMAP and OSUM—are being re-implemented using High-Level Synthesis (HLS), enabling a more modular and flexible architecture. This approach aims to improve both maintainability and performance while meeting the stringent latency and reliability requirements of the ATLAS trigger system. Ensuring the correctness of these upgrades requires a rigorous validation and simulation framework.

This thesis is dedicated to the simulation and verification of these HLS-based upgrades to the LATOME firmware. By implementing a multi-layered verification strategy, it verifies functionality and timing across increasing levels of integration. This work contributes to ensuring the reliability and performance of the LATOME firmware as part of the ATLAS Phase-I trigger upgrade. The specific objectives of this thesis are outlined in the next section.

# 1.2 Objectives

This work focuses on the HLS-based upgrades to the LATOME firmware. Its primary objectives are:

- To redesign and implement the critical REMAP and OSUM blocks of the LATOME firmware utilizing High-Level Synthesis (HLS). These components are crucial for reorganizing, processing, and aggregating real-time Super Cell data across multiple clock domains.

- To leverage HLS for enhanced development efficiency, improved maintainability, and optimized firmware performance. HLS allows for describing functionality in high-level languages, reducing development effort and promoting rapid design iteration.

- To conduct functional simulation and verification of the upgraded LATOME firmware, specifically validating the integrated HLS-based components. This involves C-level simulations and Python-based testbenches using Cocotb and QuestaSim.

- To establish and apply a robust multi-layered verification methodology, systematically addressing various levels of integration and complexity within the firmware. This includes a strategy with four distinct layers, from unit-level tests to full system simulations.

- To ensure that the LATOME firmware adheres to stringent functional and timing requirements for stable operation within the demanding environment of the ATLAS

trigger system. This objective is supported by extensive hardware validation and real-time ATLAS tests, including SOP delay calibration and CRC error monitoring.

These objectives collectively support the readiness of the LATOME firmware to handle the increased data rates and processing demands of the upgraded ATLAS trigger system.

#### 1.3 Thesis Structure

This thesis is organized into seven chapters, designed to progressively build the reader's understanding from the high-level context of the ATLAS experiment to the detailed validation results of the LATOME firmware upgrade.

- Chapter 1: Introduction. This chapter presents the motivation behind the research, outlining the technical challenges in real-time signal processing for the ATLAS experiment and the context of the firmware upgrade. It also defines the objectives of this thesis and details its overall structure.

- Chapter 2: The ATLAS Experiment. This chapter provides a broader context for the work by giving an overview of the ATLAS experiment and the Large Hadron Collider (LHC). It describes the ATLAS detector's subsystems, the role of the Trigger and Data Acquisition (TDAQ) system, and the ATLAS Detector Upgrade Program.

- Chapter 3: The Liquid Argon Calorimeter Trigger Readout Architecture. This chapter delves into the technical background of the ATLAS Liquid Argon (LAr) calorimeter and its upgraded trigger readout chain. It covers the physical structure of the LAr calorimeters, the overview of the LAr trigger readout path, the Phase-I upgrade with the introduction of Super Cells, and the design of the front-end and back-end electronics (LTDBs, LDPB, and LATOME boards). It also explains the timing and synchronization infrastructure and monitoring and real-time trigger paths essential for system operation and validation.

- Chapter 4: LATOME Firmware. This chapter describes the overall functional overview and architectural foundation of the LATOME firmware, including its various processing blocks, data flow, and clock domain organization. It also details the characteristics of the legacy firmware (Version 5), providing essential context for understanding the subsequent High-Level Synthesis (HLS)-based upgrades.

- Chapter 5: Methodology and Tools. This chapter introduces the key hardware platforms and software tools employed in this work, including Field-Programmable Gate Arrays (FPGAs) and the principles of High-Level Synthesis (HLS) using Siemens Catapult. It also presents the HLS Wrapper Generator for VHDL integration, the

Switch Matrix architecture as a foundational design pattern, and the Coroutine-Based Co-Simulation with Cocotb and QuestaSim. This chapter concludes with an overview of the multi-layered simulation and validation strategy that underpins the verification efforts.

- Chapter 6: Firmware Evolution and Validation: Versions 6.0 to 6.3. This comprehensive chapter details the evolution of the LATOME firmware from Version 6.0 to Version 6.3, outlining the architectural modifications and the corresponding simulation and validation strategies for each release. It presents the HLS-driven redesigns of key components such as the Remapping (REMAP) and Output Summing (OSUM) blocks, and their integration and validation on the monitoring and trigger paths (eFEX and jFEX). This chapter also provides a detailed explanation and application of the multi-layered simulation strategy (Layers 0 to 3), encompassing C-level simulations, RTL co-simulations, and full-firmware validation with both Firmware-Agnostic and Firmware-Aware models. Furthermore, it includes hardware tests, both in laboratory and deployed in ATLAS, particularly the SOP delay calibration campaigns and the integration of the Mini-FEX diagnostic module for real-time error observability.

- Chapter 7: Conclusion. This final chapter summarizes the main contributions of this thesis, discusses its impact on the ATLAS trigger system, and outlines potential future improvements to the firmware and validation methodologies.

# 2 The ATLAS Experiment

The ATLAS (A Toroidal LHC ApparatuS) experiment, where this work is situated, is the largest general-purpose particle detector ever built. It is operated by a collaboration of more than 5,500 scientists from 245 institutes across 42 countries [9]. The detector is designed to identify and measure the properties of particles produced in proton-proton collisions at the LHC by reconstructing their trajectories, momenta, and decay products [10]. ATLAS enables a broad physics program, ranging from precision tests of the Standard Model—including the discovery of the Higgs boson in 2012—to searches for physics beyond the Standard Model, such as dark matter candidates and extra spatial dimensions.

#### 2.1 ATLAS Overview

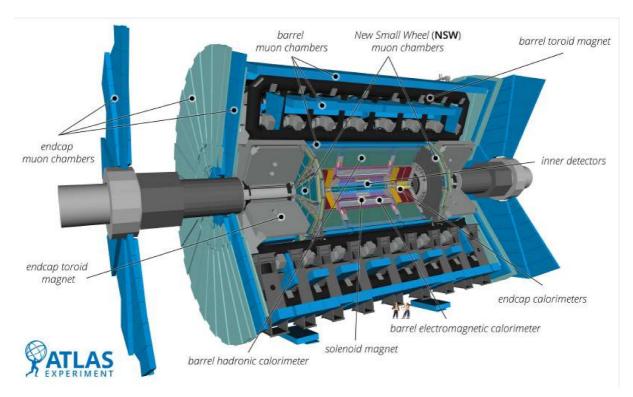

Figure 2 shows the ATLAS detector, a cylindrical structure measuring approximately 25 meters in height and 44 meters in length and weighing approximately 7000 tons. It is designed to provide nearly complete coverage around the collision point, spanning a solid angle close to  $4\pi$ . This hermetic coverage enables the precise reconstruction of particle trajectories and energy deposits across a wide range of physics processes [17].

Figure 2 – Schematic view of the ATLAS detector, illustrating its primary subsystems: the Inner Detector, Calorimeters, Magnet System, and Muon Spectrometer [11].

# 2.2 ATLAS Subsystems

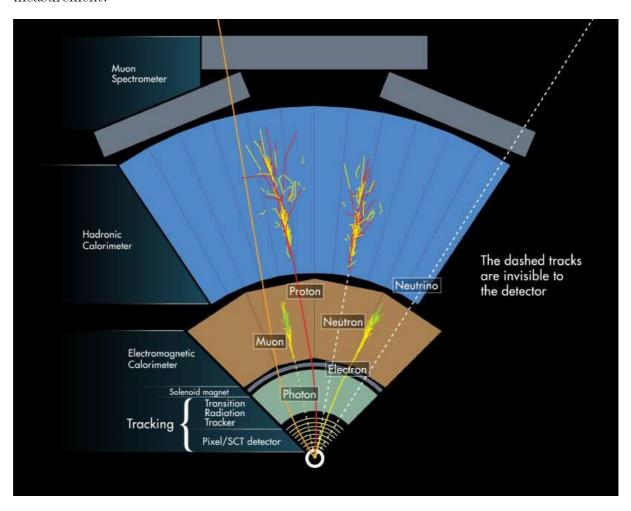

Figure 3 presents a cross-sectional view of the ATLAS detector, illustrating how various particles interact with its subsystems. The ATLAS detector consists of several concentric subsystems, each optimized for a specific role in particle detection and measurement.

Figure 3 – Transversal slice of the ATLAS detector, illustrating its primary subsystems and the typical paths of different particle types as they interact with the Inner Detector, Calorimeters, and Muon Spectrometer.

Closest to the collision point, the Inner Detector (ID) tracks charged particles with high precision, measuring their direction, momentum, and charge [12].

The Magnet System, shown in gray in Figure 3, consists of a central solenoid providing the magnetic field for the Inner Detector, and large toroidal magnets positioned around the calorimeters and muon spectrometer to enable momentum measurements of muons [13].

The Muon Spectrometer, located in the outermost layers, detects and measures the momentum of muons, which can penetrate the entire detector [14].

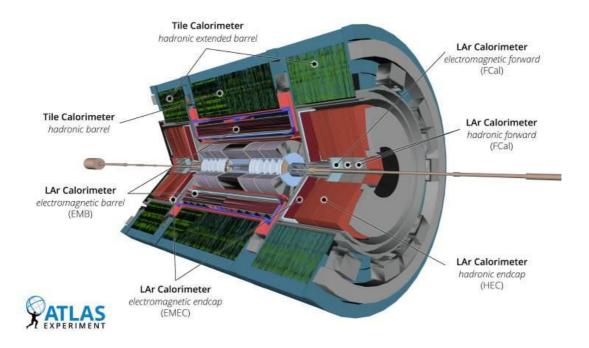

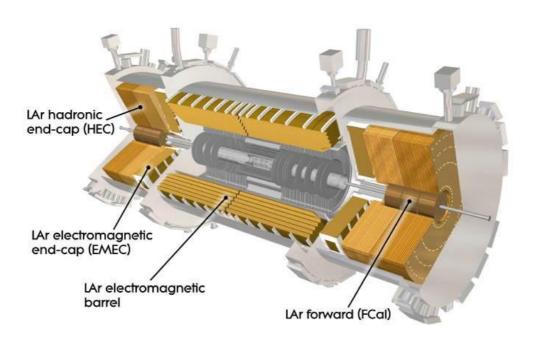

The ATLAS calorimeter system, shown in orange and blue in Figure 3 and rendered in Figure 4, is positioned between the Inner Detector and the Muon Spectrometer. It measures the energy deposited by particles as they pass through, producing ionization signals proportional to that energy. The calorimeter system consists of the Liquid Argon Calorimeter (LAr), designed to measure the energy of particles that interact electromagnetically, such as electrons and photons, and the Tile Calorimeter (TileCal), which measures the energy of particles undergoing hadronic interactions, such as protons, neutrons, and pions [15].

In addition to its role in offline physics analysis, the calorimeter system provides critical input to the Level-1 (L1) trigger — a hardware-based system responsible for rapidly selecting potentially interesting collision events in real time. This capability relies on accurate and fast energy measurements from the calorimeters. The next section discusses how this functionality is implemented within the Trigger and Data Acquisition (TDAQ) system.

Figure 4 – Cut-away view of the ATLAS calorimeter system, comprising the Liquid Argon electromagnetic calorimeters and the Tile hadronic calorimeter.

# 2.3 ATLAS Trigger and Data Acquisition System (TDAQ)

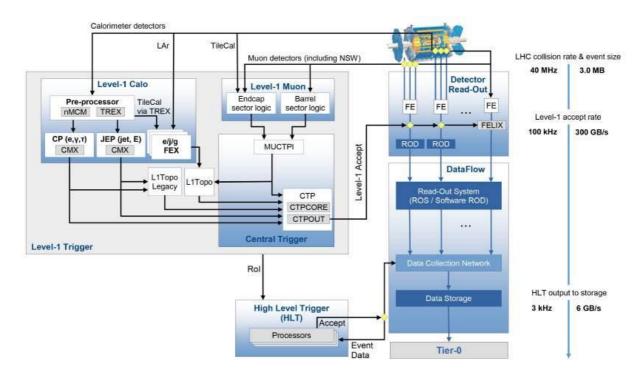

Figure 5 provides an overview of the ATLAS Trigger and Data Acquisition (TDAQ) system, which handles the large data volume produced by LHC collisions. Proton bunches cross at a frequency of 40 MHz, known as Bunch Crossings (BC), where each crossing can potentially produce one or more proton-proton collisions. Each bunch crossing occurs

every 25 ns, aligned with the LHC's 40 MHz collision frequency. The resulting data volume far exceeds the storage and processing capabilities of conventional systems [16].

Figure 5 – Overview of the ATLAS Trigger and Data Acquisition (TDAQ) system, showing the data flow from detector readout through the Level-1 hardware trigger and the High-Level software trigger to offline storage [16].

To manage this challenge, ATLAS employs a sophisticated filtering architecture designed to identify and retain only the most relevant events for physics analysis. The data processing is divided into two stages: *online* and *offline*. Online processing occurs in real time and is responsible for selecting events during collisions, while offline processing occurs after data recording and involves detailed analysis using advanced reconstruction algorithms. Offline processing includes full event reconstruction, calibration, alignment corrections, and detailed physics analysis, performed after data recording.

The TDAQ system reduces data through a multi-level filtering strategy that progressively decreases the event rate while preserving essential physics information. It is structured into two main levels:

• Level-1 (L1) Trigger: A hardware-based filtering stage that processes data from the calorimeters and muon detectors. Operating with a fixed latency of 2.5  $\mu$ s, it reduces the event rate from 40 MHz to approximately 100 kHz. A key component is the Level-1 Calorimeter Trigger (L1Calo), which receives data from the electromagnetic and hadronic calorimeters and identifies high-energy electromagnetic showers, hadronic jets, and global event quantities for early event selection [16].

• **High-Level Trigger (HLT)**: A software-based stage that receives events selected by L1. It applies full event reconstruction and more sophisticated selection algorithms to further reduce the event rate to about 3 kHz, storing only the most relevant events for offline analysis [16].

A key input to the L1Calo system comes from the upgraded Liquid Argon (LAr) calorimeter. Signals from the calorimeter are digitized by the front-end electronics and processed in real time by the back-end trigger readout system, including the LATOME boards, which prepare the energy information used by the Level-1 trigger. The processed data is then transmitted to the L1Calo Feature Extractors—eFEX, jFEX, and gFEX—which identify electromagnetic clusters, jets, and global event properties for triggering purposes.

This hierarchical filtering system, combining both real-time and offline analysis, is essential for the success of the ATLAS experiment, allowing researchers to select rare physics signals while discarding the majority of non-relevant collision events.

# 2.4 The ATLAS Detector Upgrade Program

The ATLAS Phase-I upgrade was designed to prepare the detector for the higher luminosity conditions of Run 3 and beyond. This program involved upgrades to several subsystems, including the muon detectors, the forward proton system, and the trigger and data acquisition (TDAQ) infrastructure. A key component of this effort was the upgrade of the Liquid Argon (LAr) calorimeter trigger readout, which is the focus of this thesis.

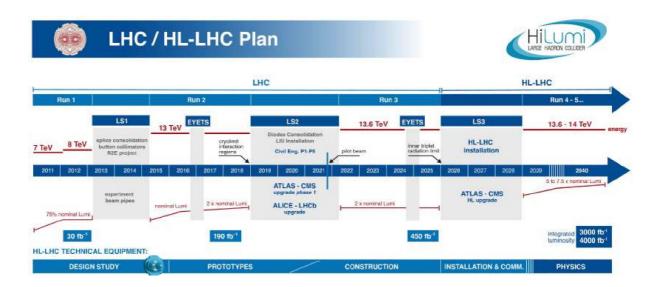

The LHC follows a structured schedule alternating between Runs and long shutdowns, as shown in Figure 6. Each Run corresponds to an operational phase of the accelerator, delivering proton-proton collisions for data collection by experiments. In contrast, a long shutdown is a planned maintenance and upgrade period, during which major technological improvements are implemented to prepare the LHC and its detectors for the next operational cycle.

The LHC began its first operational cycle, Run 1, from 2010 to 2013, reaching a center-of-mass energy of up to 8 TeV and leading to the discovery of the Higgs boson. After Long Shutdown 1, extensive hardware upgrades allowed Run 2, from 2015 to 2018, to operate at a center-of-mass energy of 13 TeV, significantly increasing the dataset available for precision measurements and new physics searches.

Following the conclusion of Run 2, the LHC and its experiments, including the ATLAS detector, entered Long Shutdown 2 in December 2018. Over the next years, critical upgrades were implemented as part of the Phase-I upgrade program. These improvements aimed to maintain trigger efficiency and detector performance under the higher pile-up conditions expected in Run 3 and the future High-Luminosity LHC (HL-LHC) era.

Figure 6 – Timeline of the LHC operational schedule, including Runs, Long Shutdowns, and the transition to the High-Luminosity LHC (HL-LHC) [21].

Among these, the LAr calorimeter received a major trigger readout upgrade. This enhancement replaces the previous analog summing approach with a fully digitized readout, providing higher spatial granularity in the calorimeter data for the Level-1 trigger system. This change significantly improves event selection capabilities, allowing the trigger to operate reliably at higher luminosities while maintaining the precision of energy measurements at the trigger level.

A detailed examination of the Liquid Argon calorimeter, the architecture of its upgraded trigger readout system, and the motivation for the firmware development presented in this thesis is provided in the following chapter.

# 3 The Liquid Argon Calorimeter Trigger Readout Architecture

The Liquid Argon (LAr) calorimeter system is a critical component of the ATLAS detector, providing high-resolution energy measurements that are essential for both offline physics analysis and real-time trigger decisions. This chapter presents the architecture of the LAr trigger readout chain, with a focus on the back-end electronics where the firmware development and validation described in this thesis are implemented.

The chapter begins with an overview of the physical structure and segmentation of the LAr calorimeter, which is essential for understanding the data organization, channel mapping, and firmware configuration. This is followed by a description of the data flow from the calorimeter to the Level-1 Calorimeter Trigger (L1Calo) and the Front-End Link eXchange (FELIX) systems. The Phase-I upgrade and the introduction of Super Cells are then discussed, providing the context for the increased data granularity that drives the architecture of the upgraded readout chain. These descriptions are intended to contextualize the operation and design of the back-end processing system—the Liquid Argon Digital Processing Blade (LDPB) and the LATOME boards—which are responsible for real-time energy reconstruction, data formatting, and delivering the processed information to the trigger and data acquisition systems. The chapter concludes with descriptions of the front-end electronics, the timing and synchronization infrastructure, and the monitoring paths that ensure coherent operation and enable real-time validation of the system.

Together, these sections provide the operational and architectural background necessary to understand the firmware development, the High-Level Synthesis (HLS) upgrades, and the validation methodologies presented in this thesis.

# 3.1 Structure of the LAr Calorimeters

The ATLAS Liquid Argon (LAr) calorimeter is a sampling detector designed to measure the energy of electromagnetic particles—such as electrons and photons—and hadronic particles in the forward region. Its geometry and segmentation directly influence the design of the trigger readout and the firmware processing chain described in this work. It operates by alternating layers of passive absorber material with active liquid argon gaps. Particles traversing the detector produce ionization in the liquid argon, which is then collected by electrodes and converted into electrical signals proportional to the deposited energy.

The LAr calorimeter is divided into four distinct detector regions, each optimized for different pseudorapidity ranges and physics goals, as illustrated in Figure 7:

• Electromagnetic Barrel (EMB) — Covers the central region of the detector ( $|\eta| < 1.475$ ). It is responsible for precise energy measurements of electrons and

photons produced near the interaction point.

- Electromagnetic Endcap (EMEC) Extends the coverage to the forward regions (1.375  $< |\eta| < 3.2$ ), maintaining high resolution for electromagnetic showers at larger pseudorapidities.

- Hadronic Endcap Calorimeter (HEC) Positioned behind the EMEC, it measures hadronic showers from strongly interacting particles, providing complementary coverage to the TileCal in the central region.

- Forward Calorimeter (FCAL) Covers the extreme forward region (3.2 <  $|\eta|$  < 4.9), where particle fluxes are highest. It is designed to withstand high radiation and measure both electromagnetic and hadronic energy.

Figure 7 – Diagram of the ATLAS Liquid Argon Calorimeter, showing its four main regions: EMB, EMEC, HEC, and FCAL.

The geometry of the calorimeter features fine segmentation in both lateral  $(\eta - \phi)$  and longitudinal layers, optimized for particle identification, energy resolution, and pile-up mitigation. The electromagnetic calorimeters (EMB and EMEC) consist of multiple longitudinal layers with different granularity: a finely segmented front layer for shower position determination, a middle layer for the bulk of energy measurement, and a coarse back layer to capture shower leakage.

This segmentation is not only crucial for offline physics reconstruction but also directly impacts the design of the trigger readout system. The mapping of calorimeter cells into Super Cells (SCs), the channel distribution into front-end and back-end electronics, and the configuration of firmware processing blocks are all intrinsically tied to the calorimeter geometry. Different detector regions have different numbers of Super Cells, data rates, and processing requirements, which are reflected in both the hardware and firmware architecture of the trigger readout chain.

The following sections present the architecture of the trigger readout system, providing the operational context for the back-end processing and firmware development described in this thesis.

# 3.2 Overview of the LAr Trigger Readout Path

The Liquid Argon (LAr) calorimeter provides real-time transverse energy measurements and digitized Super Cell (SC) data to the ATLAS Level-1 (L1) trigger system and data acquisition. This information is essential for event selection, allowing the trigger to identify electromagnetic clusters, hadronic jets, and global event properties such as missing transverse energy  $(E_T^{miss})$ , while simultaneously ensuring that the raw digitized signals are available for detector monitoring and full event reconstruction.

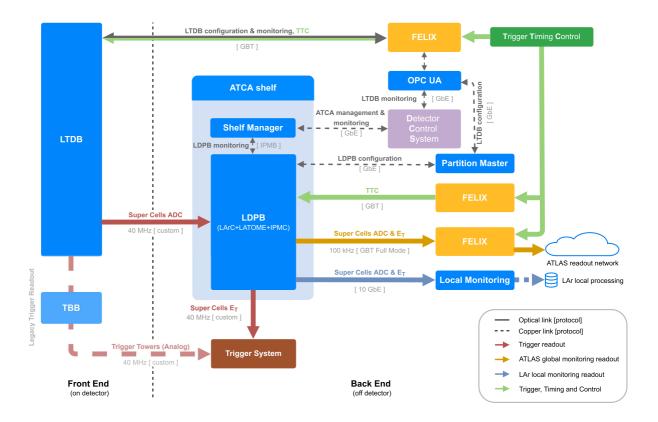

As illustrated in Figure 8, the LAr trigger readout chain consists of multiple stages. Signals generated in the calorimeter are digitized by the front-end electronics, the Liquid Argon Trigger Digitizer Boards (LTDBs), operating at 40 MHz. The digitized Super Cell (SC) data is transmitted optically to the back-end system — the Liquid Argon Digital Processing Blade (LDPB) — which hosts four LATOME boards.

The LATOME boards process the SC data in real time, performing energy calculation, basic filtering, and data formatting. The output is simultaneously transmitted to two destinations:

- The Level-1 Calorimeter Trigger (L1Calo) Feature Extractors (FEX): eFEX, jFEX, and gFEX, where the trigger decision is formed.

- The Front-End Link eXchange (FELIX) system, which handles data acquisition, detector monitoring, and validation streams.

The following sections describe the Phase-I upgrade that introduced this trigger readout architecture, as well as the implementation of its back-end and front-end electronics, the Super Cell mapping, the timing and synchronization infrastructure, and the data validation paths.

Figure 8 – The ATLAS LAr calorimeter trigger readout system. Signals are digitized by the LTDBs, processed by the LATOMEs in the back-end, and transmitted to both the L1Calo Feature Extractors (eFEX, jFEX, gFEX) for triggering and the FELIX system for data acquisition and monitoring.

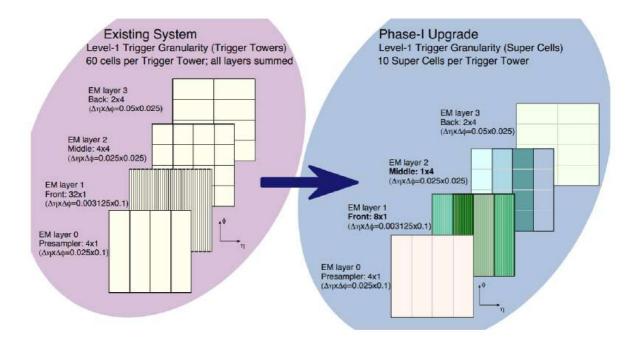

### 3.3 Phase-I Upgrade and the Introduction of Super Cells

The Phase-I upgrade of the ATLAS Liquid Argon (LAr) calorimeter introduced substantial improvements to the Level-1 (L1) trigger system, most notably by replacing the legacy Trigger Tower-based readout with a fully digital path based on high-granularity Super Cells (SCs). This enhancement increased the spatial resolution by up to a factor of ten in key calorimeter regions, enabling finer energy measurements and more selective event triggering.

In the legacy system, Trigger Towers (TTs) covered an area of  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$  and summed energy from all longitudinal layers into a single value. In contrast, SCs retain layer-specific information, with the middle layer achieving a finer granularity of  $\Delta \eta \times \Delta \phi = 0.025 \times 0.1$ . This segmentation allows for more precise reconstruction of electromagnetic showers and improves the identification of electrons, photons, and tau leptons [6].

Figure 9 illustrates this improvement. The left side shows a single Trigger Tower summing transverse energy across all layers, whereas the right highlights the enhanced segmentation of Super Cells. By maintaining separate energy measurements per layer,

SCs enable better discrimination of overlapping energy deposits and provide more detailed input to the trigger algorithms.

Figure 9 – Comparison between the legacy Trigger Tower segmentation and the Phase-I Super Cell segmentation. Super Cells provide finer granularity, preserve longitudinal layer information, and improve trigger performance.

The increase in granularity results from both longitudinal and lateral segmentation. Each Trigger Tower is typically divided into four longitudinal layers, and for certain layers — particularly the middle layer — additional lateral segmentation reduces the  $\Delta\eta$  granularity from 0.1 to 0.025 while keeping  $\Delta\phi=0.1$ . This finer segmentation directly impacts the design of the trigger readout system by significantly increasing the volume of data that must be processed in real time.

To handle this increase in data, the readout architecture was completely redesigned. The front-end Liquid Argon Trigger Digitizer Boards (LTDBs) digitize the SC signals at 40 MHz, while the back-end processors — the LATOME boards — perform real-time energy calculation and data formatting for the Level-1 trigger system and the FELIX data acquisition path. The next sections describe the implementation of these electronics and their roles in the trigger readout chain.

# 3.4 Back-End Electronics

The back-end electronics of the LAr trigger readout system are responsible for receiving the digitized Super Cell (SC) data from the front-end, performing real-time energy reconstruction, and delivering the processed information to both the Level-1 Calorimeter

Trigger (L1Calo) and the Front-End Link eXchange (FELIX) for trigger decision-making and data acquisition.

At the core of the back-end system is the Liquid Argon Digital Processing Blade (LDPB), an ATCA carrier board that hosts four Advanced Mezzanine Cards (AMCs) known as LATOMEs, as shown in Figure 10. Each LATOME is equipped with an Intel Arria 10 FPGA, which implements the full processing chain required for the trigger path.

Figure 10 – LAr Carrier (LArC) ATCA board hosting four LATOME boards.

Each LATOME receives data from 48 optical input links operating at 320 MHz. These links, connected via four MTP-12 connectors visible on the right side of the LATOME board in Figure 11, carry serialized SC data from the Liquid Argon Trigger Digitizer Boards (LTDBs). The incoming data is deserialized, realigned, and grouped by bunch crossing in the LATOME firmware to ensure proper timing and data integrity.

The real-time processing performed in the LATOME includes pedestal subtraction, basic filtering, noise suppression, and the computation of the Super Cell transverse energy  $(E_T)$ . The processed output is then formatted according to the interface specifications of the downstream systems. Data is transmitted simultaneously to the L1Calo Feature Extractors (FEX) via a MTP-48 connector located on the right side of the board, and to the FELIX system for data acquisition, monitoring, and validation.

The L1Calo FEX processors are divided into three systems:

- eFEX (Electromagnetic Feature Extractor) responsible for electron and photon identification;

- jFEX (Jet Feature Extractor) responsible for jet and tau detection;

- gFEX (Global Feature Extractor) responsible for computing global event properties, such as missing transverse energy  $(E_T^{miss})$ .

Figure 11 – A close-up view of a LATOME board, showing the heat sink, the four MTP-12 optical input connectors (green), and the MTP-48 output connector (black).

The LATOME firmware must meet latency constraints imposed by the ATLAS trigger system. All data alignment, energy computation, and output delivery occur within the fixed latency window required for the L1 trigger decision.

The next section describes the front-end electronics, which digitize the analog signals from the calorimeter and deliver the Super Cell data to the LATOME boards for processing.

# 3.5 Front-End Electronics

The front-end electronics are responsible for digitizing the analog signals generated by the LAr calorimeter and transmitting the digitized Super Cell (SC) data to the back-end system. This task is performed by the Liquid Argon Trigger Digitizer Boards (LTDBs), which are located on-detector in the radiation environment.

Each LTDB receives up to 320 analog SC signals sampled at 40 MHz. The signals are digitized with 12-bit resolution using custom radiation-hard ADCs. After digitization, the SC data is serialized and transmitted optically to the back-end electronics via 48 optical output links operating at 320 MHz.

In addition to the digital output for the upgraded trigger system, the LTDBs maintain backward compatibility by providing summed analog signals to the legacy Trigger

Tower-based system. This dual-output architecture allows for a smooth transition between the old and new trigger paths during commissioning and initial data-taking phases.

The LTDBs are designed with radiation-tolerant components to ensure stable operation in the high-radiation environment of the ATLAS calorimeter. Each board interfaces directly with the back-end LATOME boards hosted in the LAr Digital Processing Blade (LDPB), delivering the digitized SC data for real-time processing in the Level-1 trigger system.

The next section describes the timing and synchronization infrastructure that ensures coherent data transfer between the front-end and back-end electronics.

# 3.6 Timing and Synchronization

Precise timing and synchronization are essential for the operation of the LAr trigger readout system, ensuring that Super Cell (SC) data is correctly aligned to the corresponding bunch crossing (BC) and processed within the strict latency constraints of the Level-1 (L1) trigger.

The timing distribution is managed by the Trigger, Timing, and Control (TTC) system, which provides a global 40 MHz clock derived from the LHC machine clock. This clock synchronizes both the front-end and back-end electronics, aligning data sampling, digitization, and processing across the entire readout chain.

In addition to the clock signal, the TTC system distributes several critical timing commands:

- Bunch Counter Reset (BCR) resets the bunch counter at the start of each LHC orbit to ensure consistent bunch crossing identification.

- Event Counter Reset (ECR) resets the event counter, maintaining unique event identifiers within a run.

- Level-1 Accept (L1A) signals the acceptance of an event, initiating the transfer of selected data to the readout system.

These signals are distributed optically to both front-end and back-end electronics using Gigabit Transceiver (GBT) links. The LTDBs use the 40 MHz clock to sample and digitize analog SC signals synchronously with the LHC bunch crossings. The back-end LATOME boards receive the same TTC-derived clock and commands, using them to correctly describing, realign, and process the incoming SC data with deterministic latency.

This timing infrastructure ensures that data from the same bunch crossing is consistently associated throughout the readout chain, from the calorimeter front-end to the Level-1 Calorimeter Trigger (L1Calo) and the FELIX data acquisition system.

The next section describes the monitoring paths that enable real-time validation of the trigger data and ensure system integrity during operation.

# 3.7 Monitoring and Data Validation

In addition to its primary role in providing real-time energy information to the Level-1 (L1) trigger, the LAr trigger readout system incorporates dedicated monitoring paths. These paths are essential for verifying data integrity, validating energy reconstruction, and ensuring the overall performance of the system during operation.

Two main monitoring streams are implemented in the back-end electronics:

- Global Monitoring Path A Full Mode data stream from the LATOME to the Front-End Link eXchange (FELIX). This stream includes both the raw digitized ADC values and the computed transverse energy  $(E_T)$  for each Super Cell. It allows real-time validation of the energy reconstruction performed in the firmware by comparing the raw inputs with the processed outputs.

- Ethernet-Based Monitoring Path A separate path connected via a 10 Gigabit Ethernet (GbE) link from the LATOME to a dedicated monitoring server. This path provides flexible, user-configurable access to internal signals, firmware debug information, and status registers, offering a complementary tool for online debugging and validation.

The Global Monitoring Path is crucial for ensuring consistency between the online trigger data and the offline reconstructed data. By capturing both the ADC inputs and the processed  $E_T$  values, it allows the system to detect potential discrepancies caused by firmware errors, hardware faults, or data corruption.

The Ethernet-Based Monitoring Path enhances the system's operability by offering access to diagnostic information without interfering with the main trigger or data acquisition streams. This includes features such as firmware counters, data alignment status, error flags, and live snapshots of internal processing blocks.

These monitoring infrastructures are critical not only for detector commissioning and firmware development but also for long-term operations, providing the tools necessary to maintain data quality and system reliability under the demanding conditions of high-luminosity LHC running.

This chapter has detailed the architecture of the Liquid Argon trigger readout system, from signal generation in the calorimeter to real-time data processing in the back-end LATOME boards. While this overview focused on the hardware and data flow, the focus of this thesis resides in the LATOME firmware itself.

The next chapter presents the internal architecture of this firmware, describing how it handles data de-serialization, alignment, energy calculation, and output formatting. It also discusses the evolution of the firmware from version 6.0 to 6.3, highlighting the design changes and upgrades that directly motivated the validation work described in this thesis.

### 4 LATOME Firmware

This chapter describes the internal architecture of the LATOME firmware, focusing on its functional blocks and how data is received, processed, and transmitted. Each block is responsible for a specific stage in the data path, from input processing to output formatting.

The discussion begins with an overview of the firmware's functional responsibilities and data flow organization, followed by a detailed description of its clock domains and processing pipeline. The firmware is structured into four functional blocks: the Input Stage (IS), Remap (ISM), User Code (UC), and Output Summing (OSUM), each responsible for a distinct step in the data path. In addition, support components manage monitoring, slow control, and timing synchronization.

The chapter also details the characteristics of the legacy firmware (Version 5), providing essential context for understanding the subsequent High-Level Synthesis (HLS)-based upgrades. This technical foundation is essential for understanding the firmware and the validation strategies discussed in the following chapters, particularly the comprehensive evolution and validation of firmware versions 6.0 to 6.3 which are presented in Chapter 6.

#### 4.1 Firmware Functional Overview

The LATOME firmware performs real-time processing of Super Cell data in the ATLAS LAr calorimeter trigger readout chain. It receives digitized input from 48 high-speed optical links connected to the Liquid Argon Trigger Digitizer Boards (LTDBs), processes the data for each LHC bunch crossing, and delivers transverse energy  $(E_T)$  values to the Level-1 Calorimeter Trigger (L1Calo) Feature Extractors (FEXes) and the Trigger and Data Acquisition (TDAQ) system.

The main data path is implemented through four sequential processing stages:

- 1. **Descrialization and De-scrambling:** The firmware converts serialized 12-bit ADC data from each optical input into parallel data streams, aligns them temporally, and prepares them for processing.

- 2. **Geometry-Based Remapping:** The incoming SC data is reorganized into logical groupings that reflect the detector geometry. This remapping step simplifies downstream processing and aligns the data layout with the expectations of the FEX algorithms.

- 3. Transverse Energy Calculation and Bunch Crossing Tagging: Digital filtering techniques are applied to each SC to compute its transverse energy  $(E_T)$ , while

associating each measurement with the correct bunch crossing identifier (BCID), synchronized to the LHC's 25 ns cycle.

4. Output Summing and Formatting: The processed  $E_T$  values are optionally summed (for jFEX and gFEX paths), encoded, and formatted into structured data frames. These are then transmitted at fixed latency to the L1Calo and FELIX systems.

In addition to the main trigger path, which transmits real-time  $E_T$  data to the L1Calo, the LATOME firmware also supports a parallel monitoring and data acquisition (TDAQ) path. This path provides raw and processed SC data for event readout, diagnostics, and validation.

To ensure reliable operation, the firmware includes additional support modules for:

- Clock Management and TTC Decoding: Ensures alignment with the LHC timing structure by decoding the 40 MHz clock and control signals (BCR, ECR, L1A) distributed by the ATLAS TTC system.

- Slow Control Interface: Enables remote configuration, register access, and status monitoring via the IPbus protocol.

- Monitoring Infrastructure: Allows continuous access to internal signals and data streams through dedicated Ethernet and FELIX-based links, facilitating real-time validation and debugging.

These auxiliary systems are integrated alongside the main data path and are critical for maintaining synchronization, enabling configuration and control, and supporting continuous performance validation across all operating conditions.

### 4.2 Firmware Architecture

The LATOME firmware is organized into four functional blocks, each corresponding to a specific stage in the processing pipeline. These blocks operate under a pipelined architecture to meet the fixed latency and high-throughput constraints of the ATLAS Level-1 trigger system.

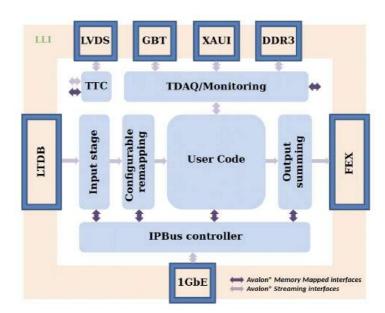

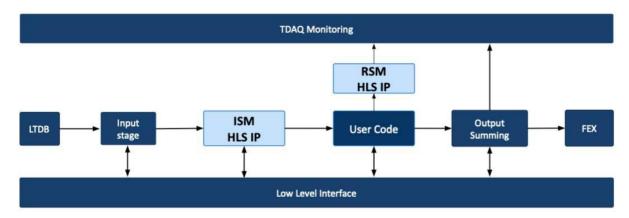

Figure 12 shows the high-level organization of the firmware, with the main data path spanning from the LTDBs to the Feature Extractor (FEX) output links. The main data path is structured as follows:

• Input Stage (IS): Descrializes and de-scrambles 12-bit ADC samples from 48 optical input links at 320 MHz. It aligns the SC data temporally and ensures synchronization across channels.

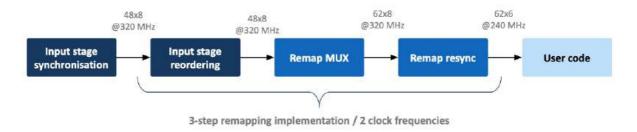

- Configurable Remapping: Reorganizes the data received from the Input Stage (IS) at 320 MHz, mapping Super Cell information into Trigger Towers according to the geometry of the detector for each bunch crossing. The reorganized data is then transferred to the User Code block operating at 240 MHz. Given that the spatial arrangement of Super Cells varies across the detector, the remapping block is configured individually for each of the 116 LATOMEs during initialization.

- User Code (UC): This block processes the Super Cell data provided by the REMAP stage at 240 MHz. It computes the transverse energy  $(E_T)$  for each Super Cell using digital filters and appends the corresponding Bunch Crossing ID (BCID). The results, together with the associated data quality bits, are forwarded to the OSUM block with fixed latency for each bunch crossing.

- Output Summing (OSUM): The final aggregation stage of the LATOME processing chain. It receives, at 240 MHz, the transverse energy values and quality bits produced by the User Code, and performs regional summations according to the detector granularity required by the trigger system. These sums are then encoded, formatted, and transferred to the Feature Extractor (FEX) output fibers at 280 MHz. Similar to the REMAP, its configuration is defined during initialization for each of the 116 LATOMEs based on the detector geometry.

Figure 12 – LATOME firmware block diagram. The pale brown frame corresponds to the hardware interface, while the blue boxes represent higher-level functional blocks [6].

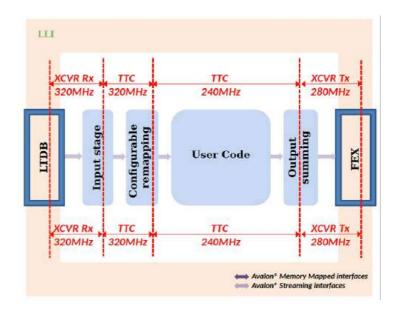

Figure 13 illustrates the three clock domains used in the LATOME firmware, which separate the high-speed input stage, the processing logic, and the output serialization. This organization reflects the functional requirements of the trigger path and ensures proper synchronization between stages.

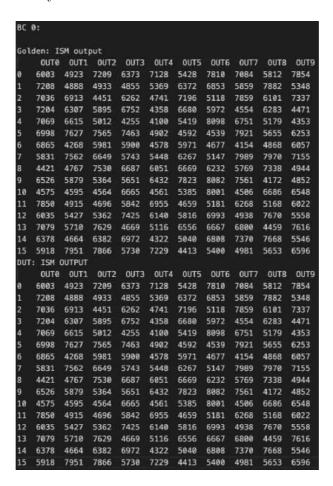

Figure 13 – LATOME firmware clock domains block diagram [6].